Other Parts Discussed in Thread: DRA72

Tool/software: Linux

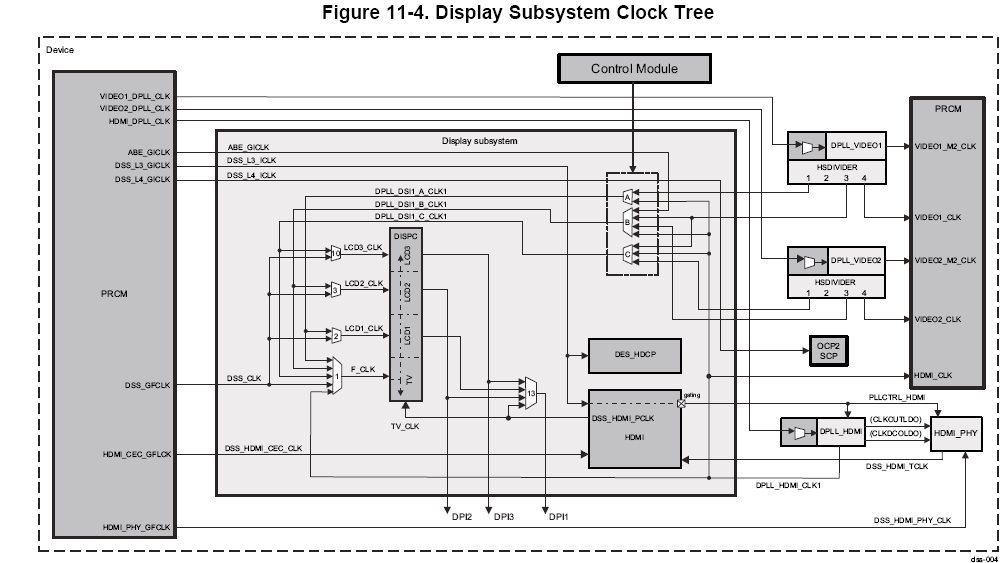

hi,I met a problem.My project required to support two lcd displays,vout1 is enable to support lcd1 output on default,so i try to enable the vout2 to support lcd2 alone at first,but i did'nt work.I have upload some files in the attatchment.The pinmux configuration is in the dts.txt,the IO_delay configutation is in the mux_data.txt,I also run the dss_dumclocks.sh to get some message,I am so confuse that while read from DSS_CTRL ,that i find some trace like that "DPI1 output : HDMI",as you can get the detail messages from the dss_dumclocks.txt in the attachment.what's more,after i run the dmesg,i find some message like that "omap_crtc_flush() timeout" 、"registered panic notifier" and etc.I am totally new guy to TI DSS system,can you give me some help?Thank you very much!