Other Parts Discussed in Thread: SYSBIOS

Hello Team,

This Support is concerning an infotainment project relating to CAN communication with TI-J6 M4 Core.

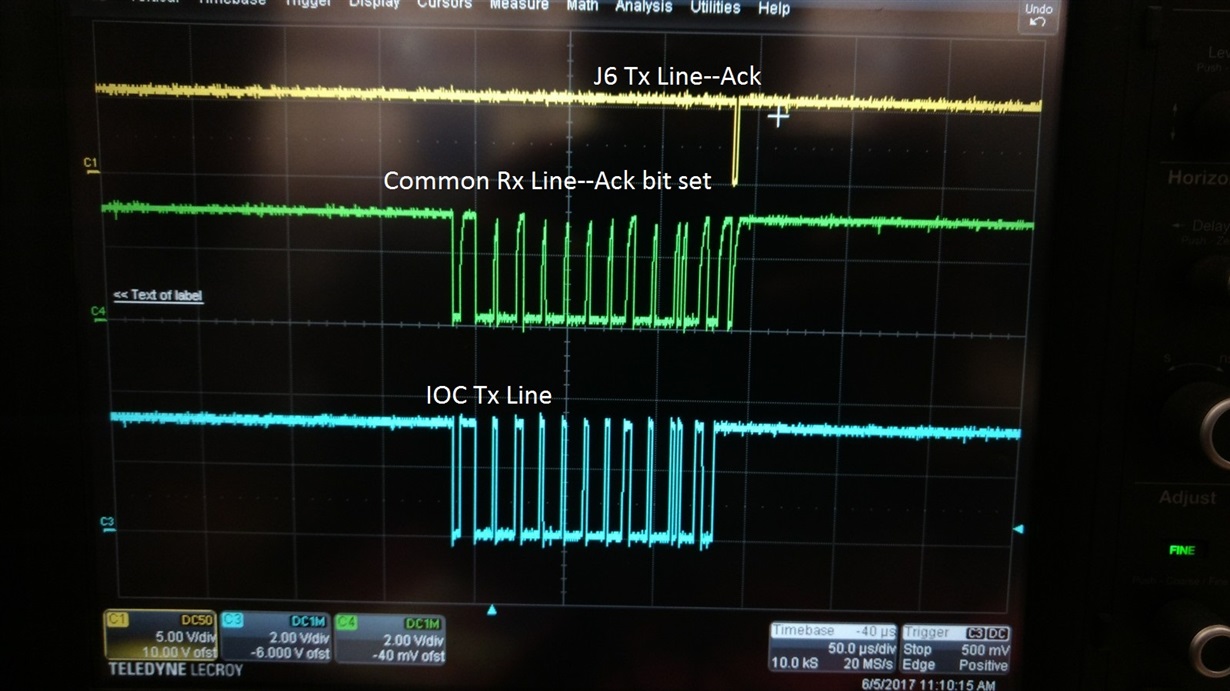

Currently in our project the CAN messages are being seen over the CAN Rx lines of J6 M4 Core. But, the J6 M4 core is not able to receive these messages meaning no interrupt is being triggered by the CAN controller.

We see that the J6-M4 core is acknowledging (Refer Image for more details where in the J6 Tx line is being acknowledged).the messages but unfortunately no interrupt is being triggered by the CAN CELL.

Even though the message is acknowledged by J6 it is not passed on to the upper layers, could you please help us out here on what could be the issue.

Thanks!

Prashanth.