Part Number: TDA3

Dear Experts,

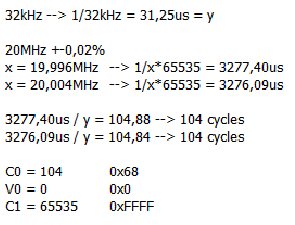

assuming the following configuration:

- Reference Clock = 32kHz ; Test Clock = 20MHz; allowed deviation of Test Clock = 0.02%

I end up with a value of "0" for Valid0 counter. I am wondering about

1) Is it allowed to have a "0" for Valid0 or is at least a "1" value necessary for Valid0 counter in this case?

2) Is there a general limit with regards to the deviation accuracy?

Calculations:

Many thanks and best regards,

Gregor