Tool/software: TI-RTOS

Hello!

When I am debugging the MDIO interface,I encountered a strange question. I can not access the phy register.

Software and hardware environment is as follows:

bios_6_46_04_53

ndk_2_24_02_31

nsp_gmacsw_4_15_00_00

TDA2XX

Some of my analysis is as follows:

1、Use linux + bios system in tda2x, pinmux and Network driver configured in linux,mido function is OK,so I can confirm the hardware is OK.

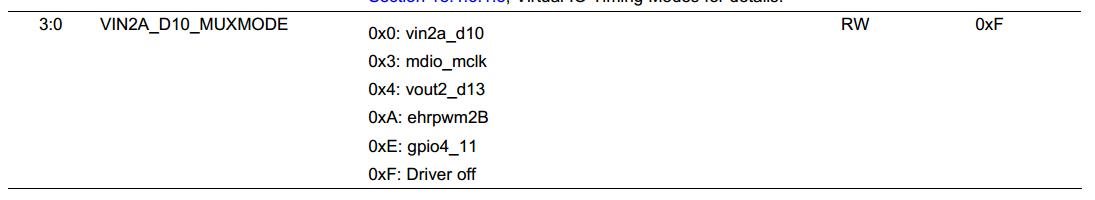

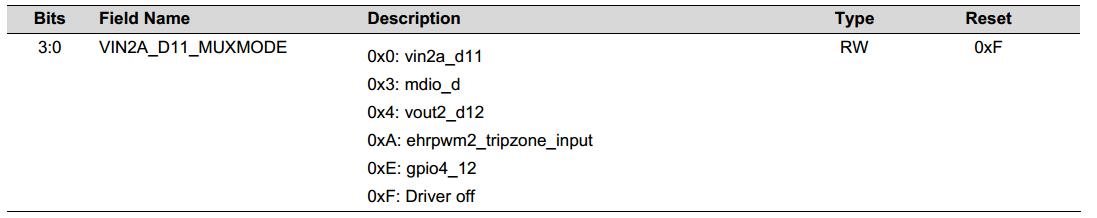

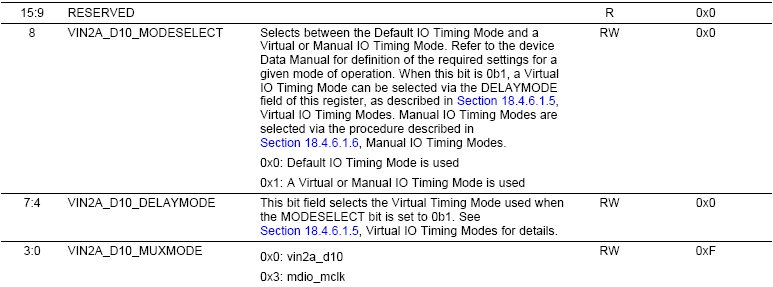

2、but only use bioss ystem, I can not access the phy register.MDIO pinmux MCLK pin is0x30003(output) ,MDIO is 0x70003(input)

3、some MDIO Register as follows:

myMDIO_VER:0x40070106

myMDIO_ALIVE:0x0

myMDIO_CONTROL:0x41000198

myMDIO_LINK:0x0

Why the MDIO_ALIVE register is always 0?

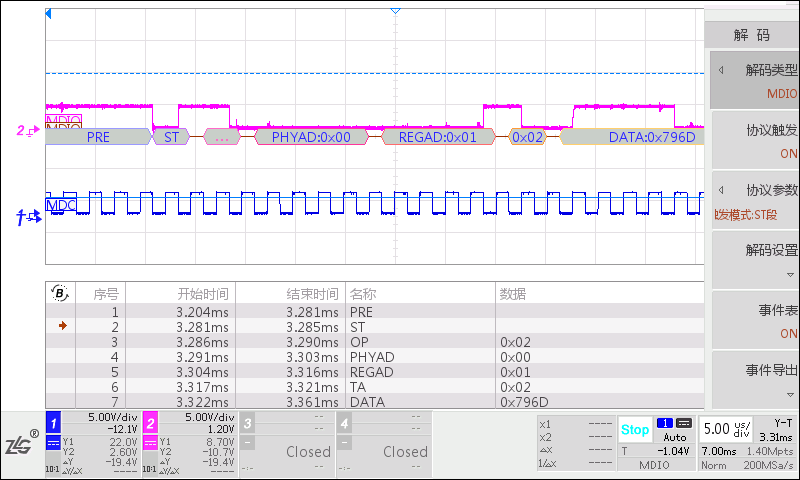

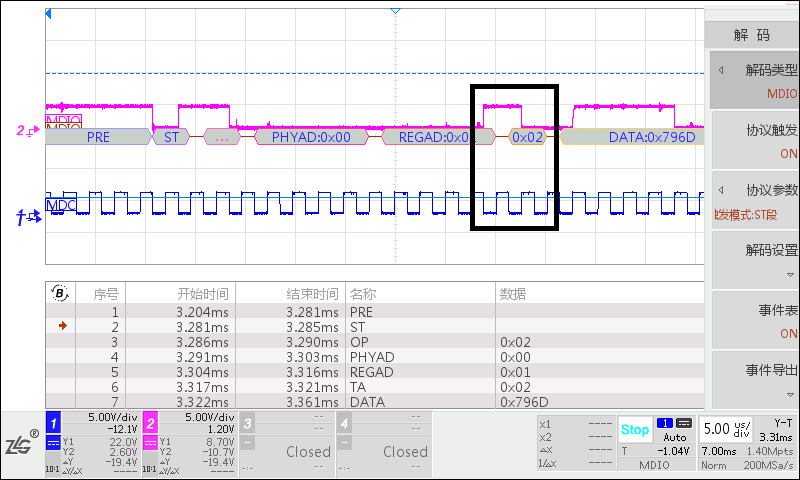

4、After the SOC is powered on,I use oscilloscope to measure the waveform of two pins of mdio:

Phy address 0 is responsive,but MDIO_ALIVE register is always 0,How can I debug it?

Thanks!