Tool/software: Code Composer Studio

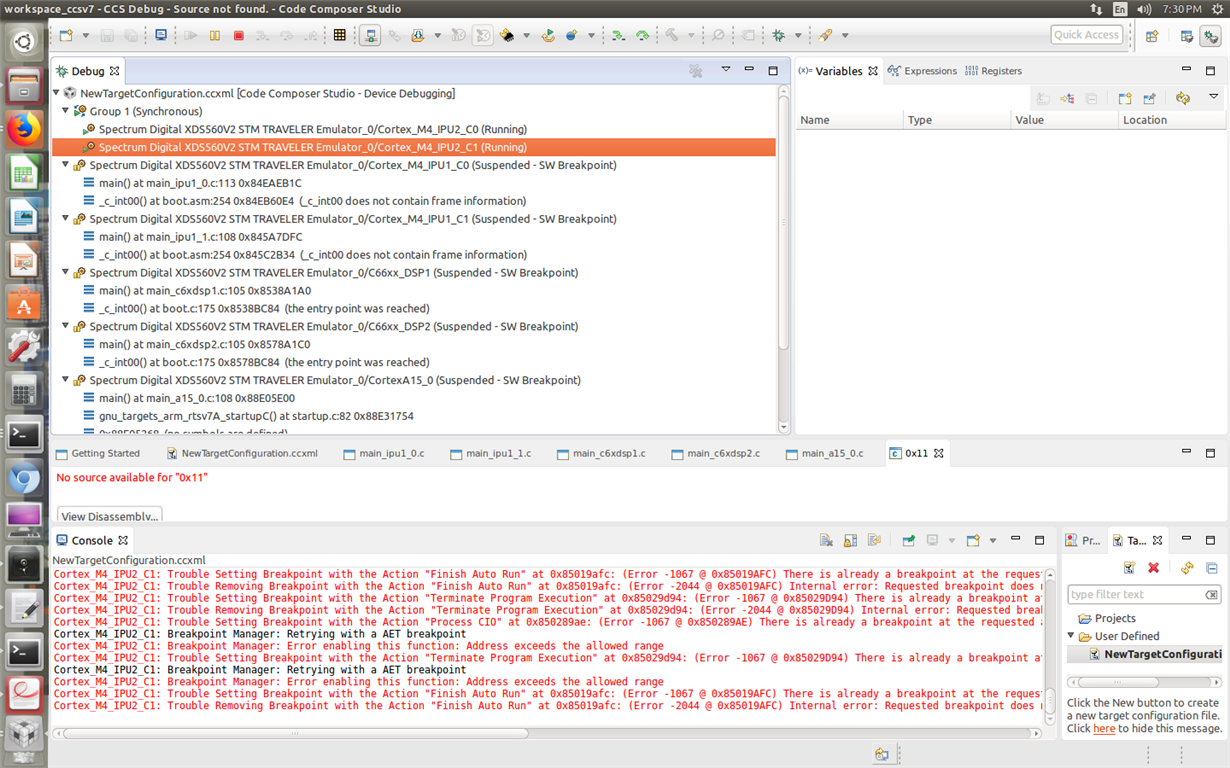

We are trying to debug the Vision SDK code on CCS, that we followed all steps mention in section "3.8 Load using CCS" of "Vision SDK TDA2xx User guide " document. and seeing expected output in CCS in debug mode but not able to see anything on UART so could not be able to run some use-case and debug the code.

Are we missing anything in this setup?

Thanks