Recently I started using AWR1243P.

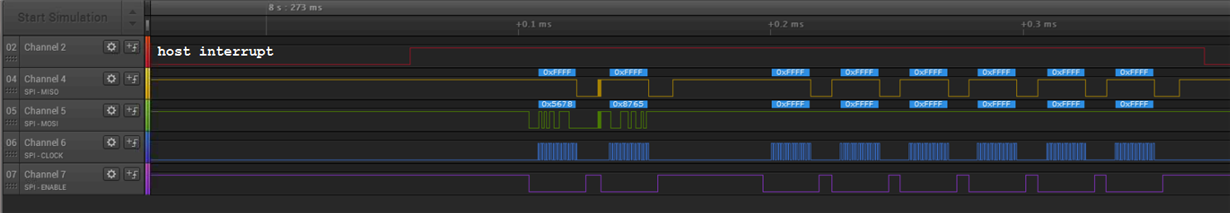

When AWR1243P starts MCSPI communication with TDA3xx, the IRQ is always HIGH and the initialization wait does not end.

Is AWR1243P different in MCSPI communication process from AWR1243?

Also , is the MCSPI of AWR 1243P communicating while IRQ is HIGH?