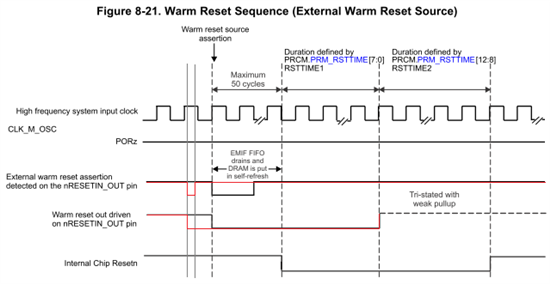

"Caution must be used when implementing the nRESETIN_OUT as an bi-directional reset signal. Because of the short maximum time allowed using RSTTIME1, it does not supply an adequate debounce time for an external push button circuit. The processor could potentially start running while external components are still in reset. It is recommended that this signal be used as input only (do not connect to other devices as a reset) to implement a push button reset circuit to the AM335x, or an output only to be able to reset other devices after an AM335x reset completes."

Above paragraph is last para of 8.1.1.7.4.1 section of AM335x TRM.

When we use push button for warmreset push button will give a reset pulse of milisec but befor completion of that pulse AM335x start asserting it own pulse outwards. We think that that would cause electrical problem and also there is chance of chip damage.

We would like to know are the I/O buffers of AM335x can handle all this for long time?

Please reply it is urgent!!!!!!!!