Hi,

I'm writing a CAN driver for the AM335x EVM and have run into an issue.

Generally, the driver works well, but when receiving over 300 frames/s of data (extended frames, DLC=8 bytes) consistently, the processor freezes and the board requires a restart. This usually happens after a few minutes of use. I have two boards back-to-back and a CAN bus analyzer in between and it's the receiver side that hangs.

The driver sets up the first message object to receive frames with any message ID (standard or extended) on the CAN bus. The second message object is used to transmit any message (standard or extended).

The receiver part of the driver does not use the rx FIFO mode and it does not use DMA.

I've been focusing my debug activities on the transfer from the receive message object to the CPU registers and I have a couple of questions:

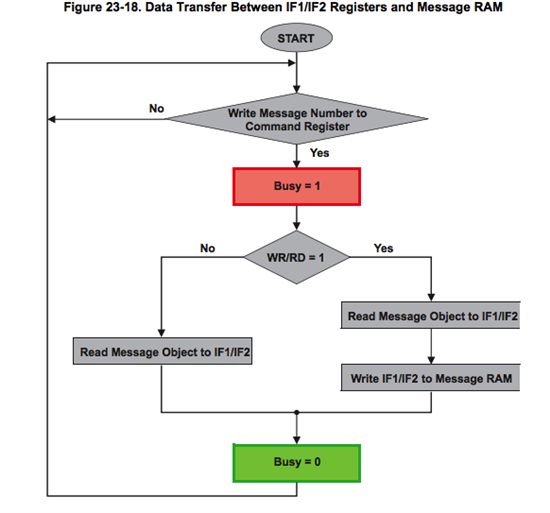

1. In spruh73k, figure 23-18, the following diagram explains the transfer steps from/to message RAM:

Can you explain the first decision box that says "write message number to command register" - what does the yes/no outcome mean? My code waits for the busy bit to clear before sending a command.

3. I want to use the IF3 register set instead so that the information is automatically updated (using IF3UPD12=1). What interrupt vector on the AM335x EVM do I need to use to get an interrupt on reception of a frame? Once I set IF3UPD12, I can see that data gets updated in the IF3 registers, but I don't get an interrupt on vectors 52, 53 or 54 anymore.

Thanks for your help.

Andre