I would like to know the following:

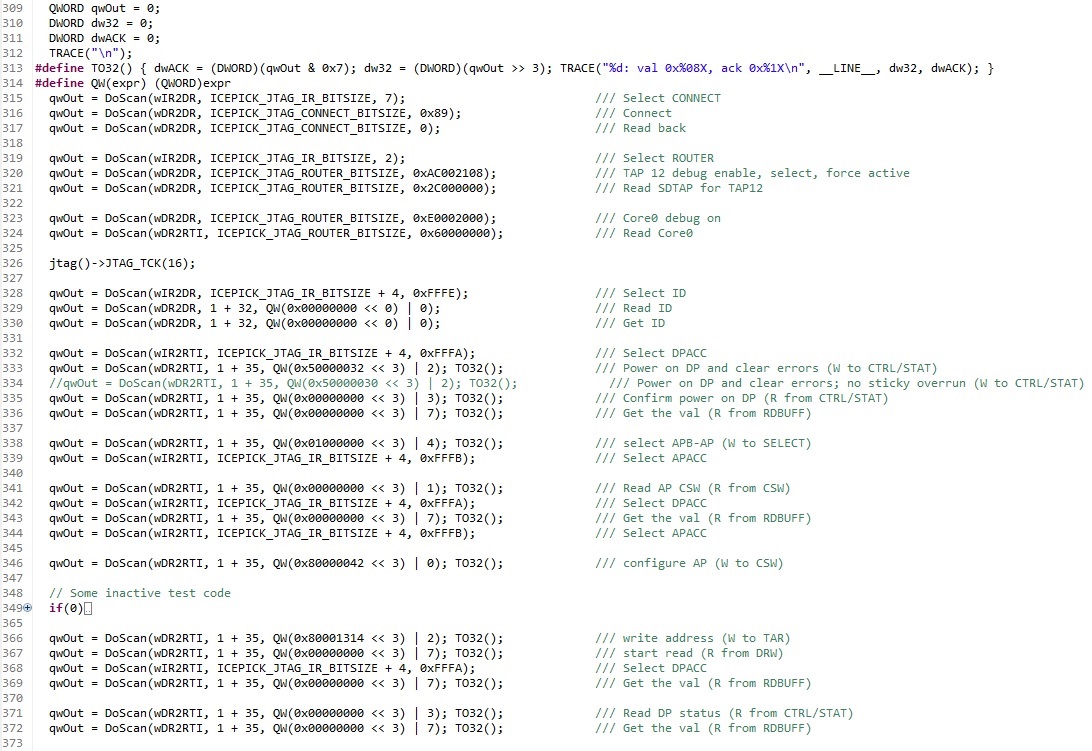

- What is the secondary TAP index in IcePick for CoreSight TAP? It was 3 on some OMAP devices.

- Memory map for CoreSight components? What are the addresses of System Debug, ETM, TPIU, ETB, etc.?

- Is ROM Table implemented at all?

- Is there an ETRM document for this devices?