The AM335x datasheet describes a 4 layer stackup of the minimum PCB stackup.

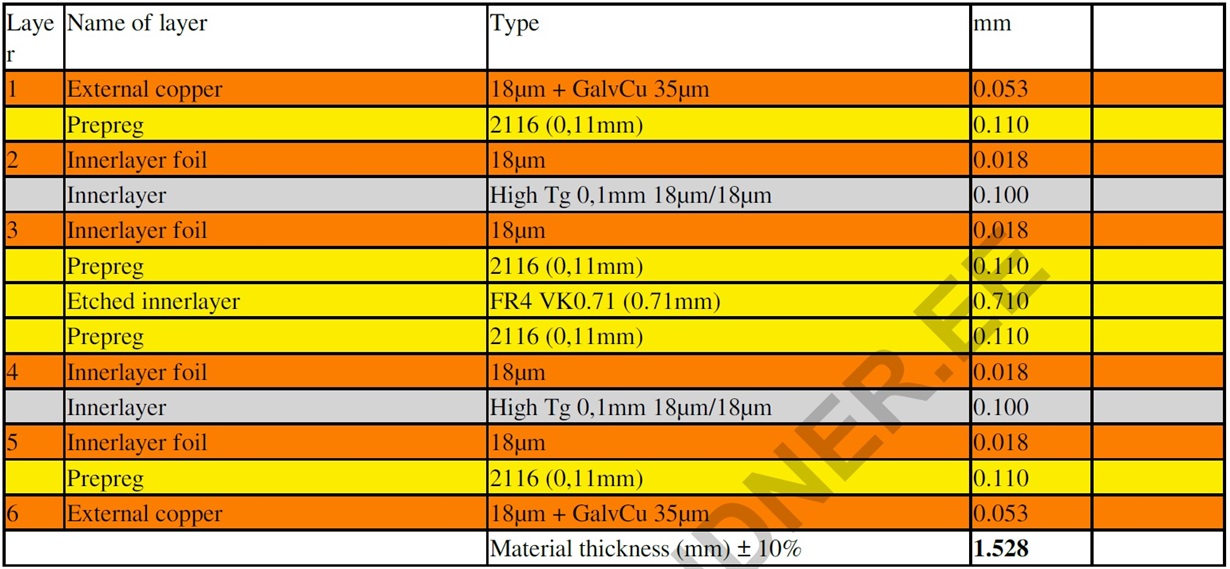

A 6 layer stackup is shown as follows.

LAYER TYPE DESCRIPTION

1 Signal Top signal routing

2 Plane Ground

3 Plane Split Power Plane

4 Signal Internal routing

5 Plane Ground

6 Signal Bottom signal routing

I understand that all of these signals should be routed first on layer 1 (Top). If it is not possible to route all of these signals on layer 1 (Top), which of layer 4 (Internal) or layer 6 (Bottom) should the remains be routed on?

Best regards,

Daisuke