According to the sleep sequencing for the AM3359, when you execute the WFI command from SRAM the PRCM_M3_IRQ2 interrupt will signal the Cortex-M3. You can see this progression in the state flow diagram at http://processors.wiki.ti.com/index.php/File:SA_deep_sleep_state_flow.JPG. When the M3 receives this interrupt, the interrupt handler function "extint34_handler" should execute since it is registered to this interrupt in the vector table. However, this never happens.

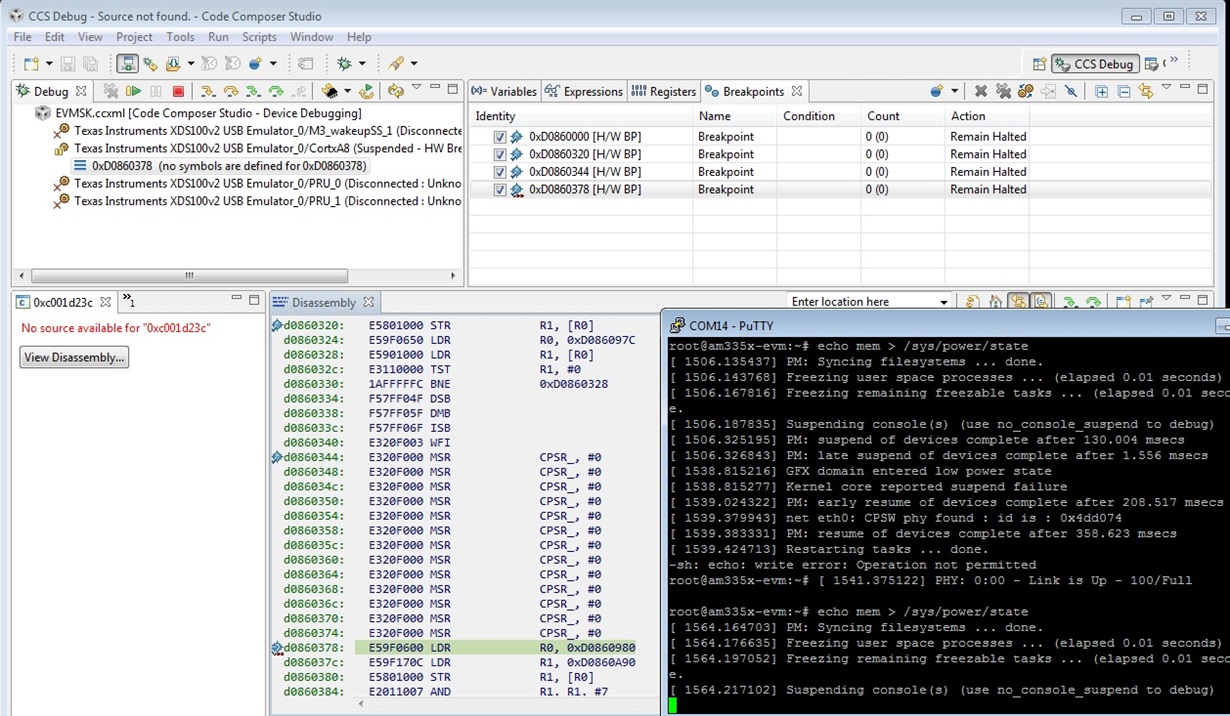

I have compiled the CM3 PM firmware sources from http://arago-project.org/git/projects/?p=am33x-cm3.git;a=summary and loaded/initialized the CM3 with the bin file successfully. I am also using an XDS100v2 JTAG emulator to connect to the M3 core and I am able to step through the code and use breakpoints. When I set a breakpoint in the interrupt handler for #34, it never hits the breakpoint, which tells me the A8 never signals it at WFI.

Up until the WFI command is executed, I am able to communicate with the firmware on the M3; it is possible to send the DS0/STANDBY commands and it acknowledges them successfully. For the A8 to signal the M3 correctly, what settings are required for this interrupt to be generated? Should it happen unconditionally, or does the A8 internally check clock settings/ power domain settings?