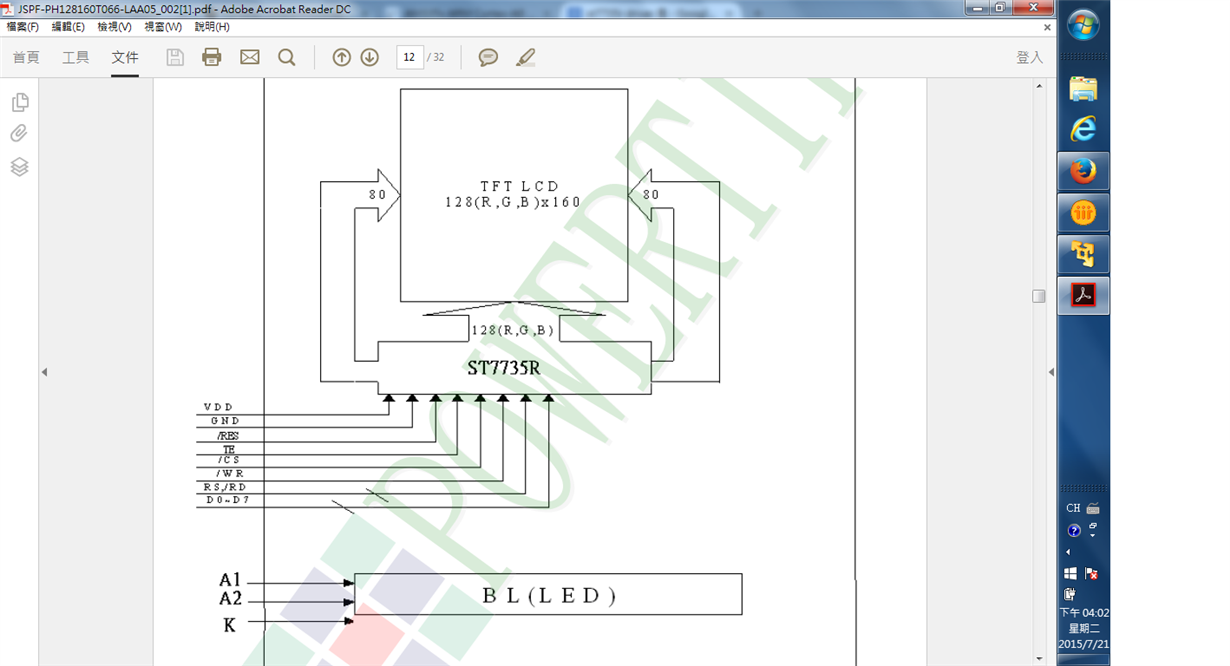

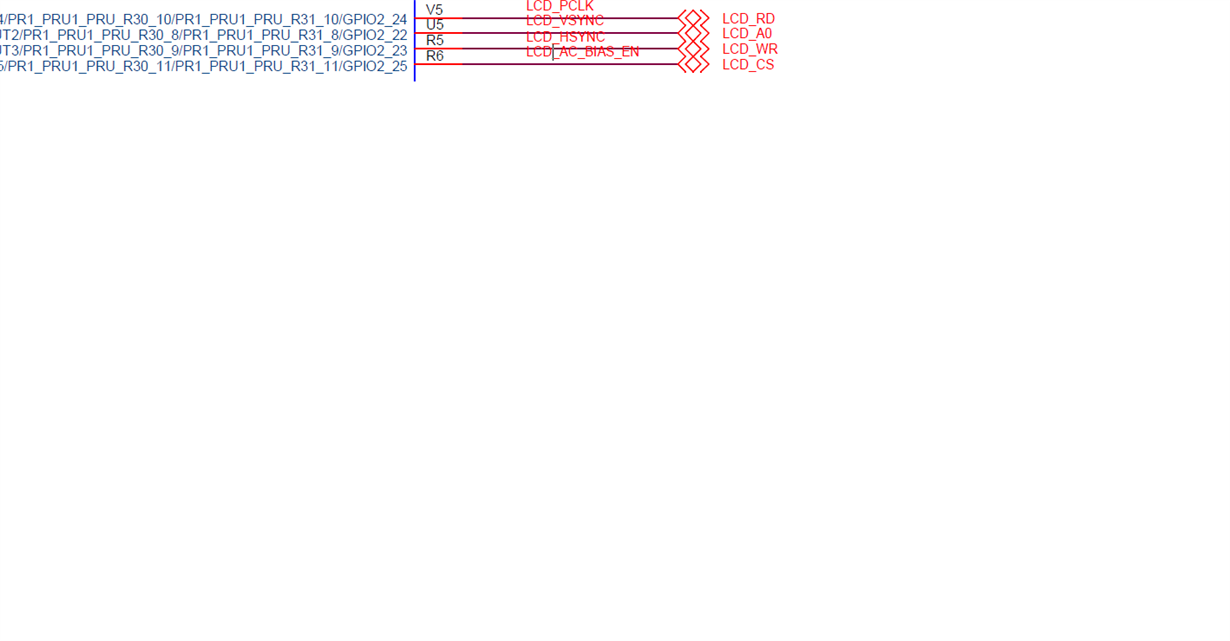

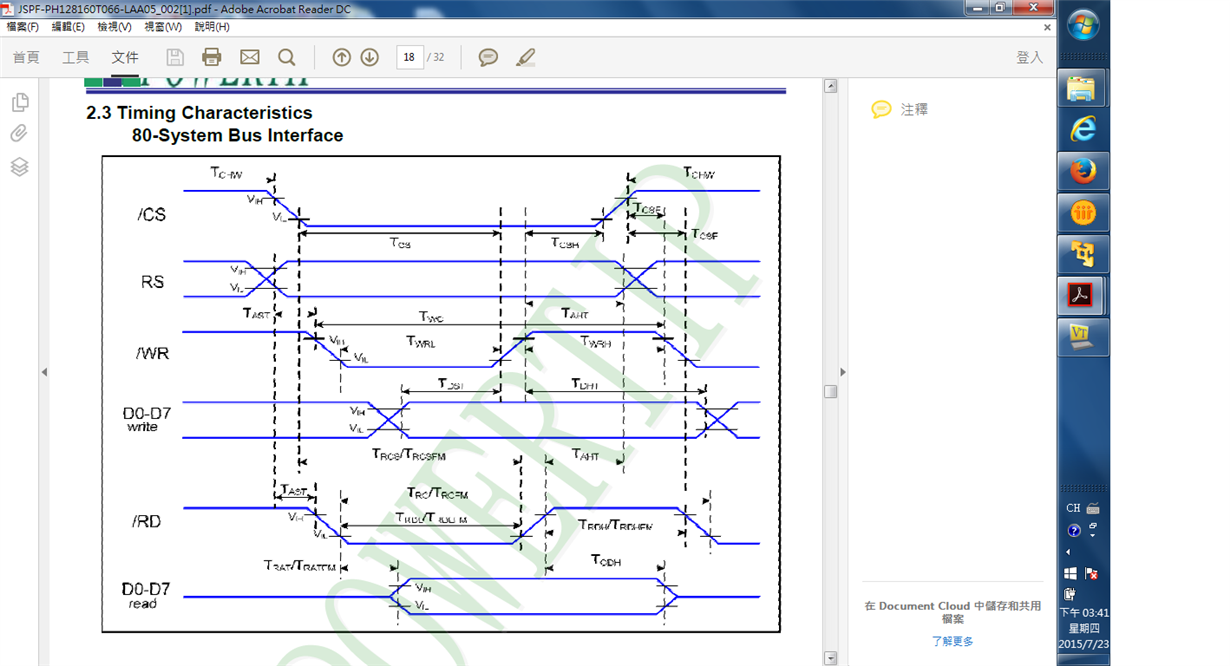

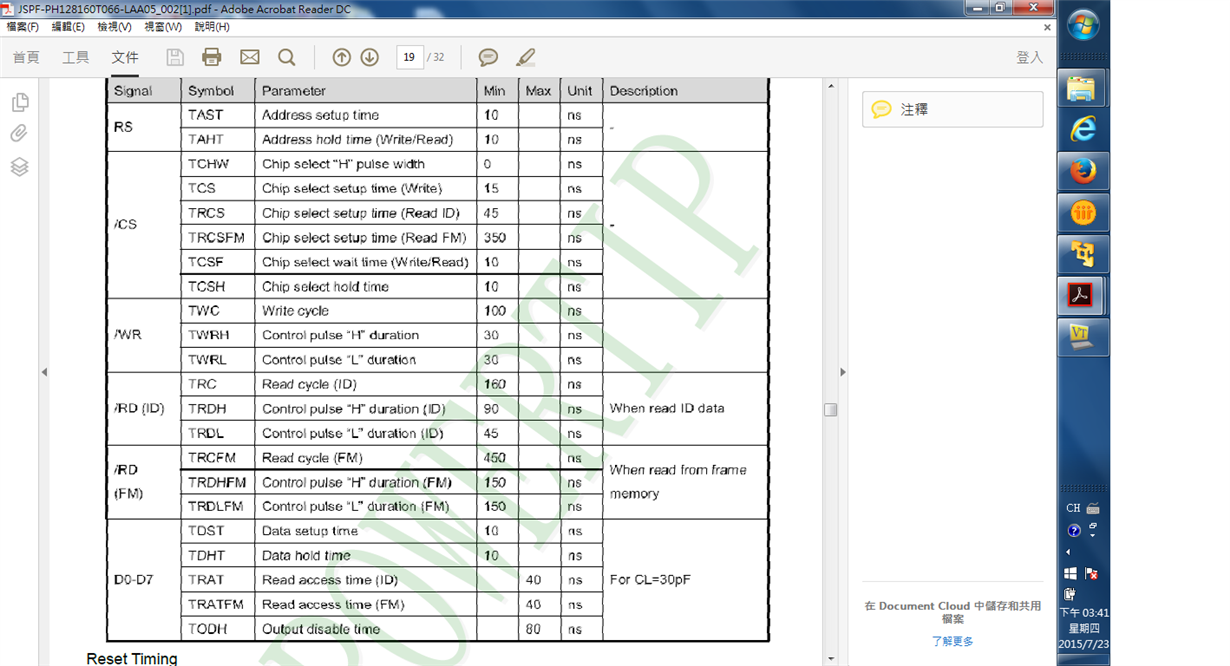

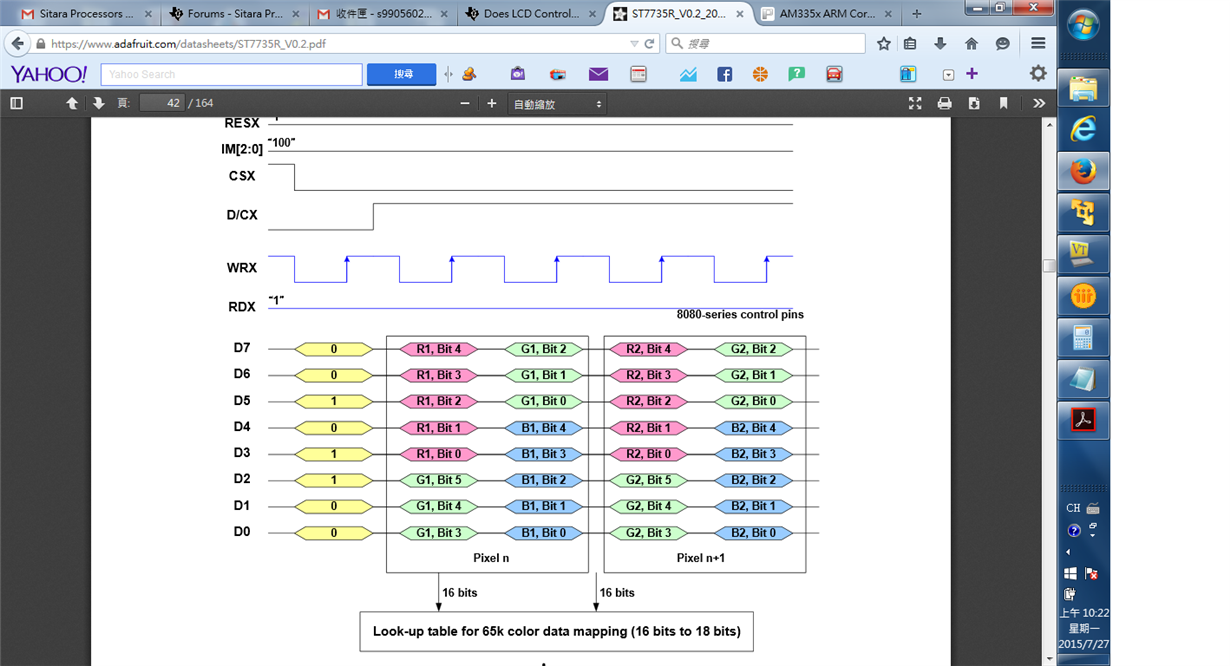

We adapt the ST7735R LCD (126*168 TFT 16bit 565 mode) 8080 mode, and I have referenced drivers/lcd Leonerdo supplies in below address and reference am335x TRM chapter 13.3.4 (LIDD controller).

BSP version: sdk6

image.h :

#ifndef CONFIG_SPL_BUILD

unsigned int const image1[] __attribute__((aligned(4)))= {

0x4000u, 0x0000u, 0x0000u, 0x0000u, 0x0000u, 0x0000u, 0x0000u, 0x0000u,

..

};

#endif

#define SOC_LCDC_0_REGS 0x4830E000

#define LCDC_CLKC_ENABLE (0x6C)

#define LCDC_RASTER_CTRL (0x28)

#define LCDC_LCD_CTRL (0x4)

#define LCDC_LIDD_CTRL (0xC)

#define LCDC_LCDDMA_CTRL (0x40)

#define LCDC_CLKC_ENABLE_CORE (0x00000001u)

#define LCDC_CLKC_ENABLE_DMA (0x00000004u)

#define LCDC_CLKC_ENABLE_LIDD (0x00000002u)

#define LCDC_RASTER_CTRL_RASTER_EN (0x00000001u)

#define LCDC_LCD_CTRL_MODESEL_LIDD (0x0u)

#define LCDC_LCD_CTRL_CLKDIV_SHIFT (0x00000008u)

#define LCDC_LIDD_CTRL_LIDD_DMA_EN_ACTIVATE (0x1u)

#define LCDC_LIDD_CTRL_LIDD_DMA_EN_SHIFT (0x00000008u)

#define LCDC_LCDDMA_CTRL_FRAME_MODE (0x00000001u)

#define LCDC_LCDDMA_CTRL_BURST_SIZE_SHIFT (0x00000004u)

#define LCDC_LCDDMA_CTRL_TH_FIFO_READY_SHIFT (0x00000008u)

#define LCDC_LIDD_CTRL_LIDD_MODE_SEL_SYNC_MPU80 (0x2u)

lidd.c:

# include "image.h"

int Lcd_Init (){

unsigned int clkDiv;

/* **Clock for DMA,LIDD and for Core(which encompasses

** Raster Active Matrix and Passive Matrix logic)

** enabled. */

HWREG(SOC_LCDC_0_REGS + LCDC_CLKC_ENABLE) = (LCDC_CLKC_ENABLE_CORE | LCDC_CLKC_ENABLE_DMA | LCDC_CLKC_ENABLE_LIDD);

/* Disable raster */

HWREG(SOC_LCDC_0_REGS + LCDC_RASTER_CTRL) &= ~LCDC_RASTER_CTRL_RASTER_EN;

/* Configure the pclk */

clkDiv = 192000000 / 23040000 ;

HWREG(SOC_LCDC_0_REGS + LCDC_LCD_CTRL) = LCDC_LCD_CTRL_MODESEL_LIDD;

HWREG(SOC_CLDC_0_REGS + LCDC_LCD_CTRL) |= (clkDiv << LCDC_LCD_CTRL_CLKDIV_SHIFT);

/* DMA enable in lidd mode */

HWREG(SOC_LCDC_0_REGS + LCDC_LIDD_CTRL) = (LCDC_LIDD_CTRL_LIDD_DMA_EN_ACTIVATE << LCDC_LIDD_CTRL_LIDD_DMA_EN_SHIFT);

/* Configuring DMA of LCD controller */

HWREG(SOC_LCDC_0_REGS + LCDC_LCDDMA_CTRL) = LCDC_LCDDMA_CTRL_FRAME_MODE | (4 <<LCDC_LCDDMA_CTRL_BURST_SIZE_SHIFT ) | (0 << LCDC_LCDDMA_CTRL_TH_FIFO_READY_SHIFT) | 0;

// Configuring the base ceiling

HWREG(SOC_LCDC_0_REGS + LCDC_LCDDMA_FB0_BASE) = (unsigned int)image1 ;

HWREG(baseAddr + LCDC_LCDDMA_FB0_CEILING) = (unsigned int)image1 + sizeof(image1) - 2;

HWREG(SOC_LCDC_0_REGS + LCDC_LCDDMA_FB1_BASE) = (unsigned int)image1 ;

HWREG(baseAddr + LCDC_LCDDMA_FB0_CEILING) = (unsigned int)image1 + sizeof(image1) - 2;

// Enable End of frame0/frame1 interrupt

HWREG(SOC_LCDC_0 + LCDC_IRQENABLE_SET) = (RASTER_END_OF_FRAME0_INT | RASTER_END_OF_FRAME1_INT);

// RasterModeConfig(SOC_LCDC_0_REGS, RASTER_DISPLAY_MODE_TFT_UNPACKED,

RASTER_PALETTE_DATA, RASTER_COLOR, RASTER_RIGHT_ALIGNED);

But panel have no picture in screen. I have two question to ask.

1 These process for initializing LIDD mode above are correct?

2 Do I need write something to initial LCD panel?

Thank you, TI.