Hi Sitara Champs!

I am quite new to McASP and sound driver development, and was hoping for some guidance to enable custom functionality.

Background

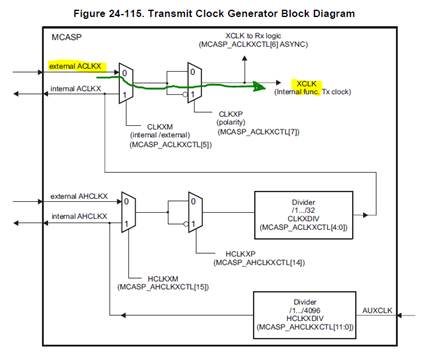

I am attempting to utilize the McASP for sending data out from an AM335x to a CPLD using gstreamer or other userspace audio application. The specific hardware configuration is different from the EVM examples in that there is no high-speed clock present, only a bit clock and frame sync being sourced externally by the CPLD to the Sitara. I was able to find quite a few posts and references to sourcing clocks to the McASP externally, but I was not able to find one with this particular configuration..

Goal

Drive a single channel of data from the McASP of the AM335x device to a CPLD with the CPLD providing bit clock and frame sync to the McASP of the AM335x utilizing gstreamer or similar userspace application.

Issue

Present analysis of the existing audio and McASP Linux drivers/examples (sound/soc/davinci/davinci-evm.c and davinci-mcasp.c) appears to indicate that an external or internal high frequency clock is required for the McASP and audio drivers to function properly. Modifications to the driver appear to be required to operate solely from an external bit clock and frame sync.

Questions

-

Is the sysclk within the davinci-evm.c sound file referencing the high-speed (AHCLK) clock of the McASP peripheral?

-

Is it possible to drive only a bit clock and frame sync to the McASP and utilize the existing audio Linux drivers and userspace applications (gstreamer) or are significant changes needed to enable this setup?

-

Can the sound driver operate without a high-speed clock source (sysclk) present on the McASP/Sitara?

Steps Taken

-

The Processor SDK Linux Audio page was utilized to perform the Audio DAC Example and to reference the Audio Porting Guide to gain some familiarity with the driver structure.

-

The existing driver configuration for BeagleBone Black (TDA998x) was used as a basis to configure the McASP being driven by the internal clock (26MHz) on the high-frequency transmit clock (AHCLKX), being divided down for the bit clock (ACLKX), and generating the frame sync internally as well. devicetree changes were made for pinmuxing.

-

Gstreamer was then utilized to feed data to the sound driver with data being shown on the serializer pin (axr1) of the custom hardware using an oscilloscope.

-

-

Changes were made to the example snd_soc_dai_link’s .dai_fmt within evm_dai_tda998x_hdmi to indicate codec bit clock master and code frame sync master for configuring the McASP as receiving both the bit clock and frame sync from the CPLD (SND_SOC_DAIFMT_CBM_CFM).

-

These changes resulted in no data being present on the serializer

-

-

After removing the above changes, changes were made to the evm_tda998x_hw_params function instead to manually set the bclk_freq and sysclk (high-speed clock) variables to match those of the CPLD inputs while still operating the McASP off internal clocks.

-

Any changes made to the bclk_freq or sysclk values resulted in no data being present on the serializer.

-

-

Having both changes present at the same time (codec bit clock/frame sync master and adjusting sysclk/bclk_freq) also resulted in no data being present on the serializer.

-

Current estimates are that since the CPLD is providing the bit clock instead of the high-speed (sysclk) this approach will not operate correctly with the current Linux driver and modifications are necessary.

Any assistance or guidance is greatly appreciated!

Best Regards,

Mark-