Dear Ti E2E community,

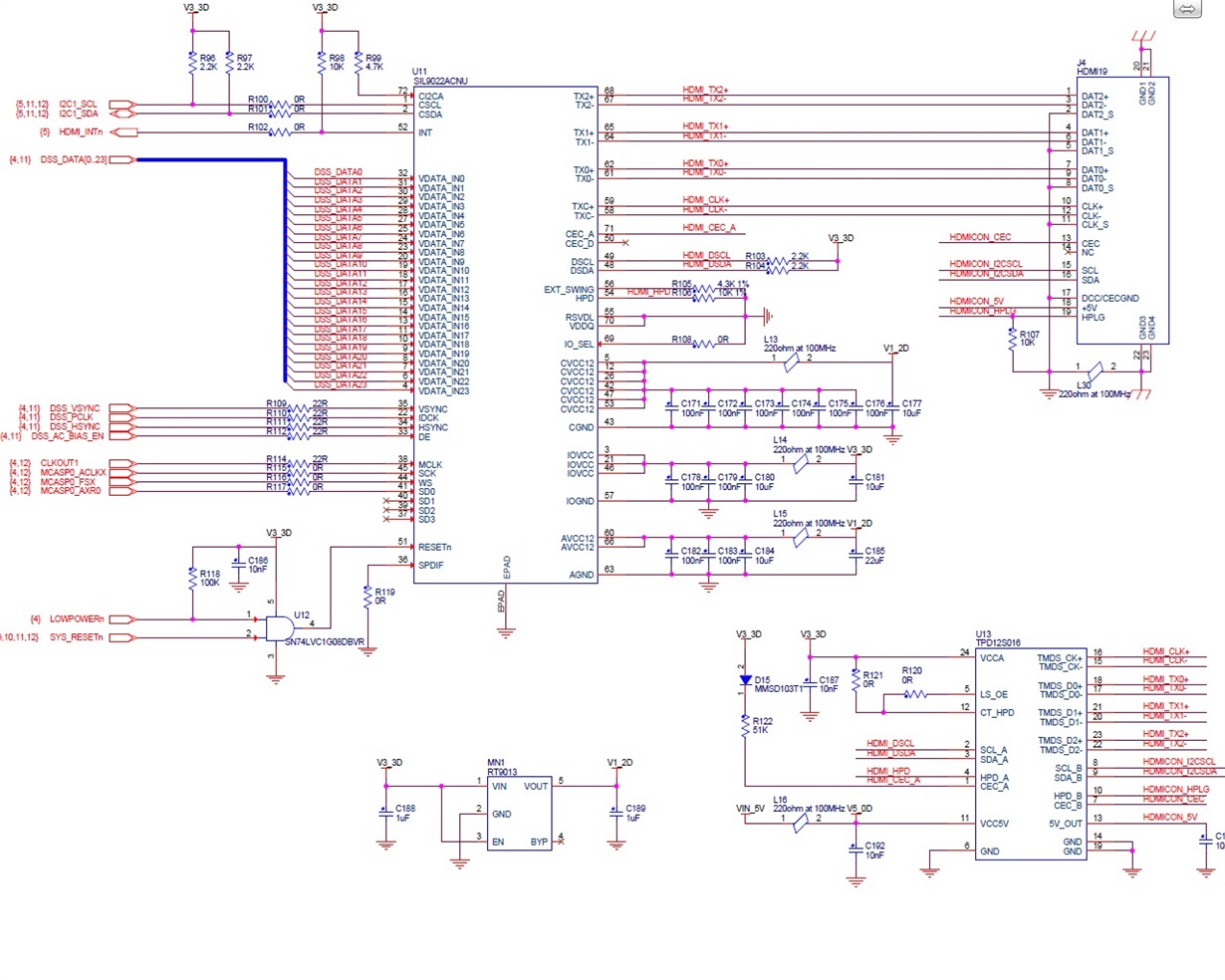

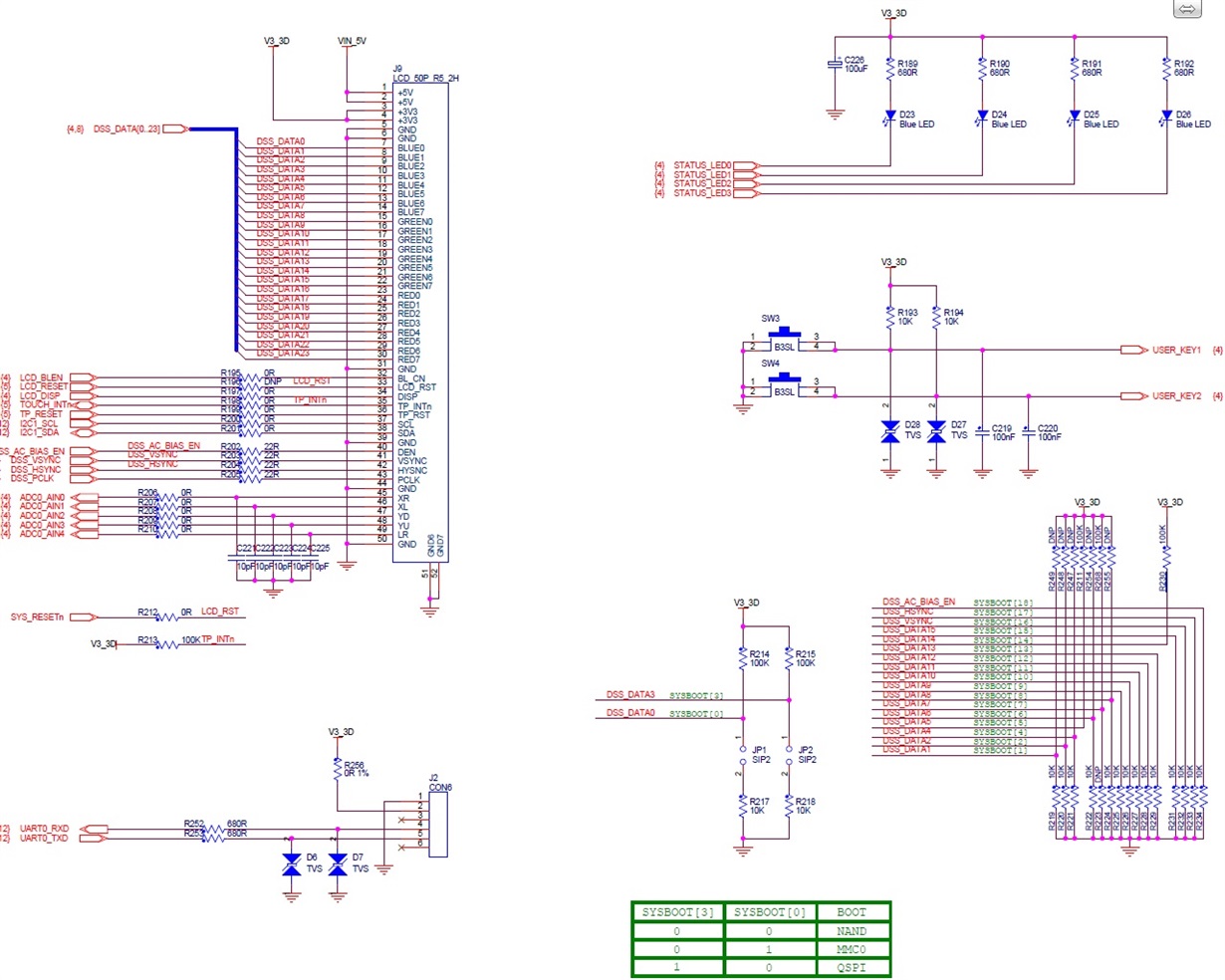

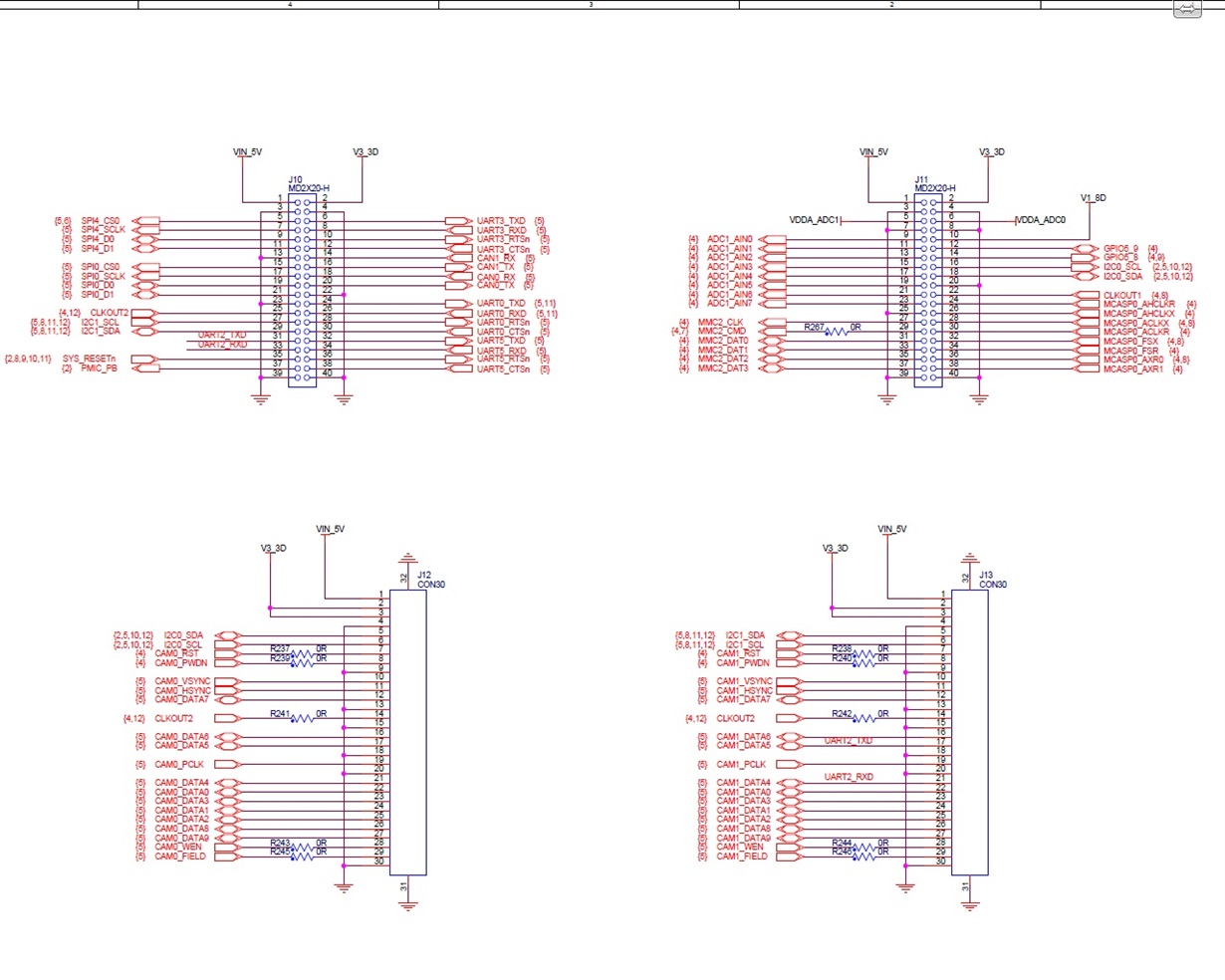

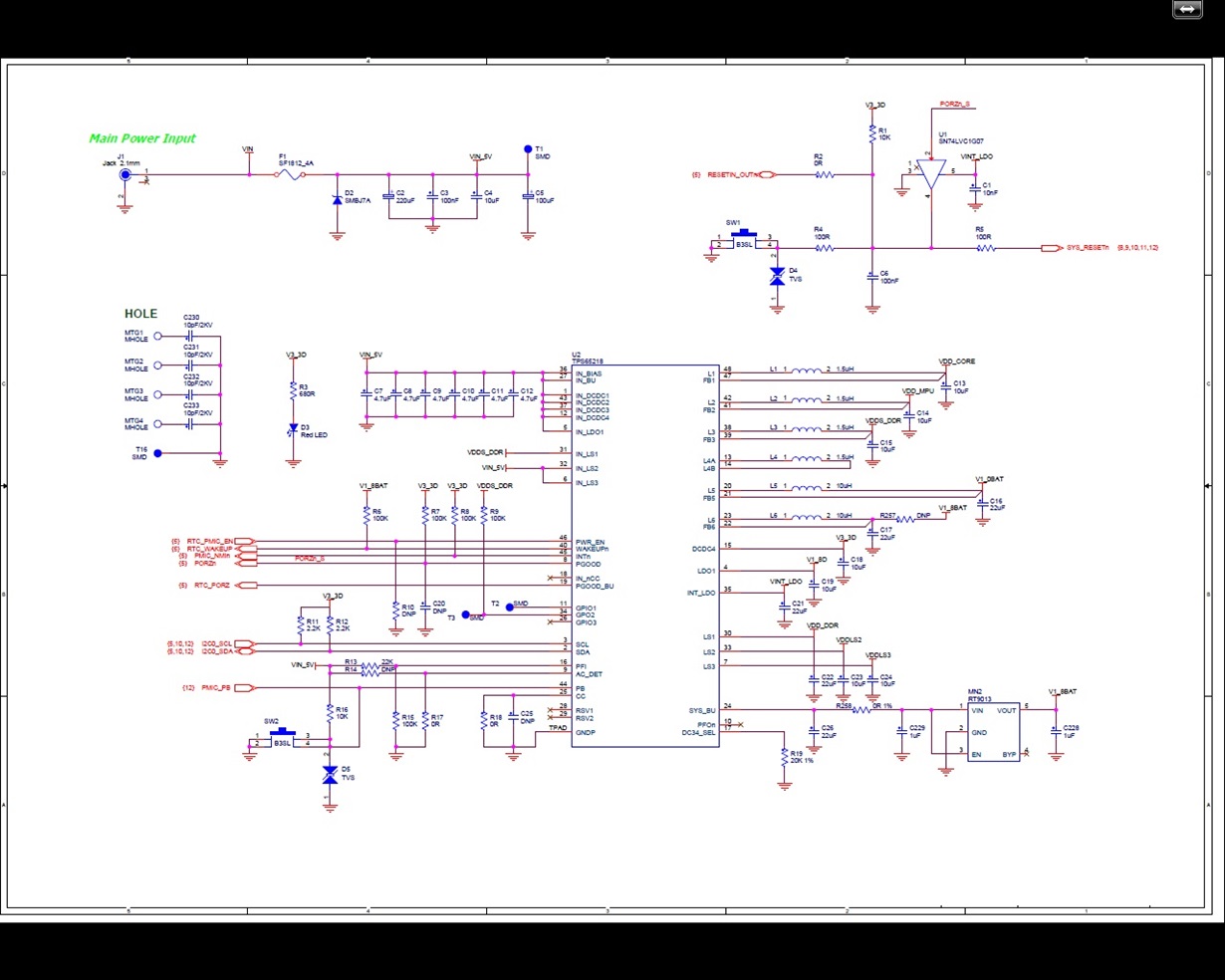

I connect Am437x Rico Board with hdmi to vga converter to LCD samsung, but no HDMI output. Please show me how to configure using for HDMI or LCD

I type on console :

root@am437x-evm:~# cat /proc/cmdline

console=ttyO0,115200n8 omapdss.def_disp=display1 omapfb.mode=display1:1024x768MR

-24@60 spi-ti-qspi.enable_qspi=1 root=/dev/mmcblk0p2 init=/linuxrc rootfstype=ext4

--> does it mean that board configured for HDMI ?

Thanks you very much