Hi~

I'm using the AM3359 ICE v2 + SDK 1.1.0.8 + Intel e1000e NIC + IgH EtherCAT master v1.5.2 and I have been testing a DC cycle in 100us sampling time.

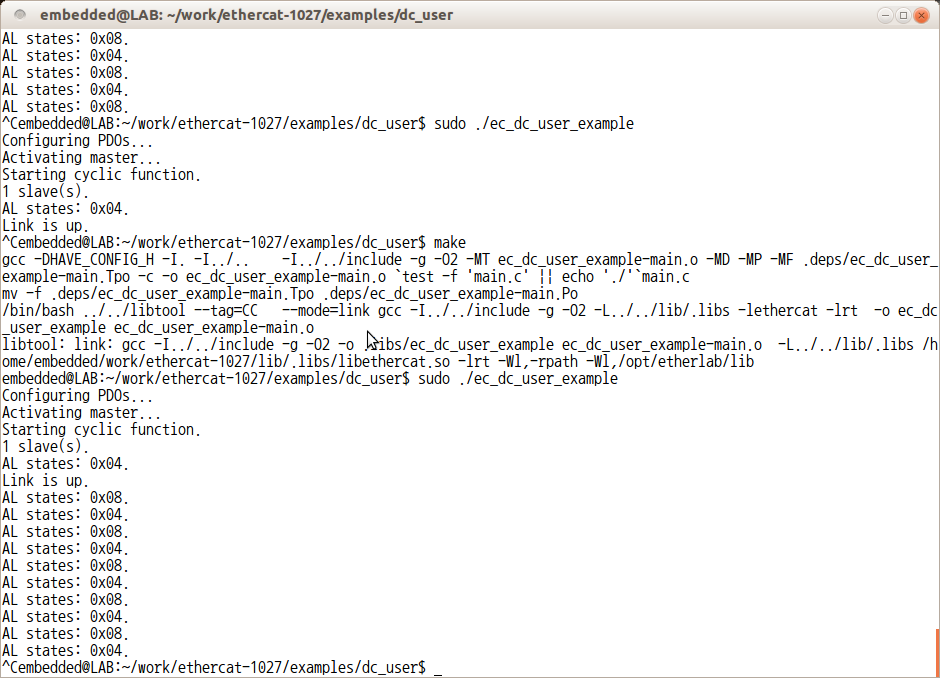

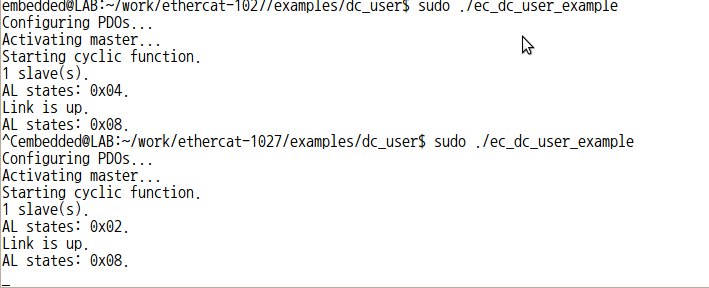

Using the IgH DC example code, the master and slaves well operated(no errors, no warnings).

I found that the IgH EtherCAT supports DC Sync1 mode. So, I checked DC related objects (0x1c32 registers).

0x1c32:02 (cycle time) : In my case 100,000(100us) ~ 500,000(500us)

0x1c32:05 (Min Cycle Time) : 31,200 (31.2us)

0x1c32:06 (Calc + Copy Time) : 0

0x1c32:09 (Delay Time) : 0

I think that the cycle time is possible in a range of 32us ~ 100us.

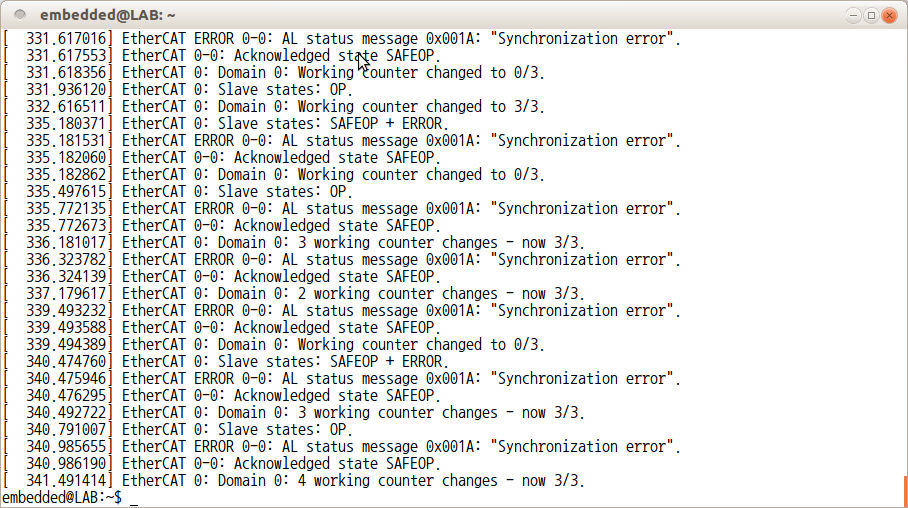

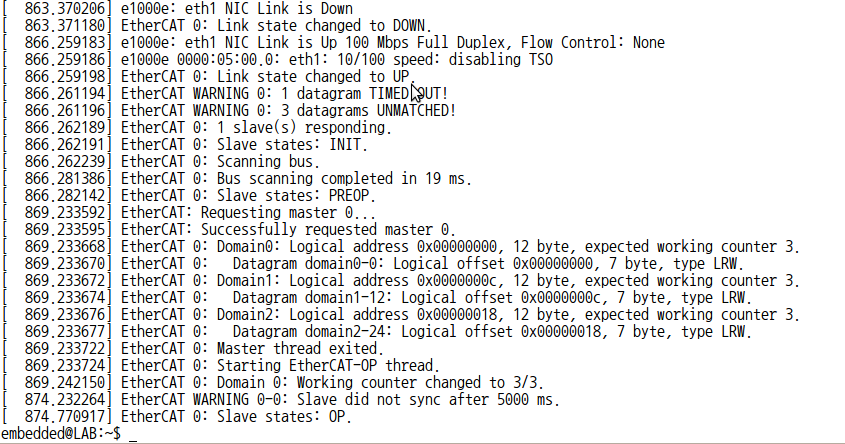

In the real test, however, DC example code with under 100us sampling time was not working. Datagram skipped message occurred.

And in the E2E community article, Frank said ICE's maximum freq is 10kHz(100us).

What is the problem? ICE hardware or SDK's restriction? if not, IgH EtherCAT master's software problem?

Regards.