Hi,

I have some questions regarding ECC function of Am57xx processor.

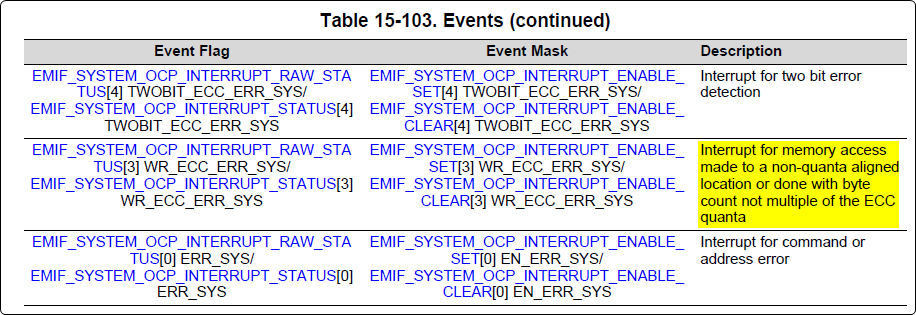

1.I would like to know how to work the ECC function.If 8bit or 16bit write access occurs, how does AM57xx work wiht ECC function? For example,

1. 32bit read

2. 8 or 16 bit write

3. ECC calculation

4. 32bit write

Is the above sequence right?

2.If the above sequence is right, there is 1bit error when 32bit reading, how does AM57xx work?

3.If there is 2bit error when 32bit reading, how does AM57xx work?

4.When 32bit write access occurs, 32bit read access does not happen because all bits is changed. Is my understanding right?

5.If 1bit error is detected by ECC function when 32bit reading, Its data is modified by ECC,isn't it? and, is the modified data writebcked after modified data sended to CPU(or other Master)?

I appreciate your quick reply.

Best regards,

Michi