Dear,

We are testing AM4377 for RGMII-1, RGMII-2 and PRU ICSS-1 interface.

We are using two PHY 's in the design one for RGMII interface and other for switching between RGMII and PRUICSS.

PHY supports both RGMII and MII and can switch between RGMII and MII interface.

We have the requirement to support the below different modes:

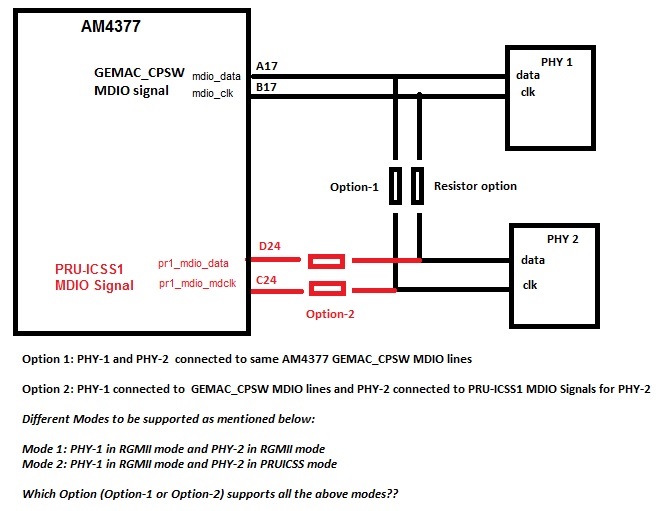

Mode 1: PHY-1 in RGMII mode and PHY-2 in RGMII mode

Mode 2: PHY-1 in RGMII mode and PHY-2 in PRUICSS mode

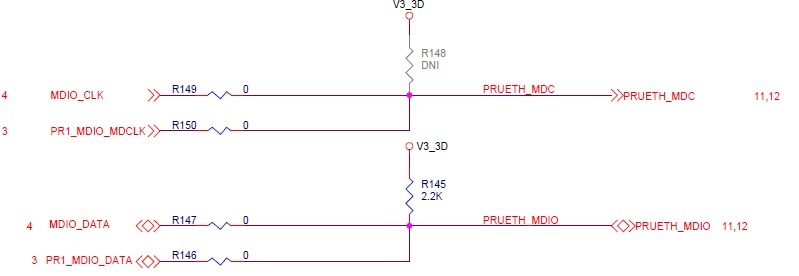

We have provided two MDIO connections for PHY as mentioned below:

Option 1: PHY-1 and PHY-2 connected to same AM4377 GEMAC_CPSW MDIO lines

Option 2: PHY-1 connected to GEMAC_CPSW MDIO lines and PHY-2 connected to PRU-ICSS1 MDIO Signals for PHY-2.

Please refer the image for Hardware MDIO connection.

Below are our queries:

1. With respect to Option 1( ie... same MDIO signals for both PHY's) , what are the different modes can be supported?

2. With respect to Option 2(ie... separate MDIO signals for each PHY), what are the different modes can be supported?

We want to know whether AM4377 software/driver can support these different modes with the above MDIO signals connected to PHY

Thank you

Regards

B. Eshak