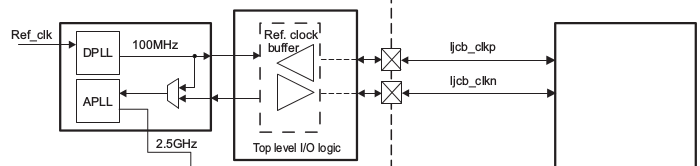

I use the kernel is 4.1.13, and I want to make ljcb_clkp and ljcb_clkn as output as the follow:

but I can't find the the device tree configuration for set these pins output, can you give me some help?

I have seen that this driver seems dosen't support this function, but what should i do for this ?

Thank you very much!

Best Regards

Qing