Other Parts Discussed in Thread: SYSBIOS

Tool/software: TI-RTOS

Hi,

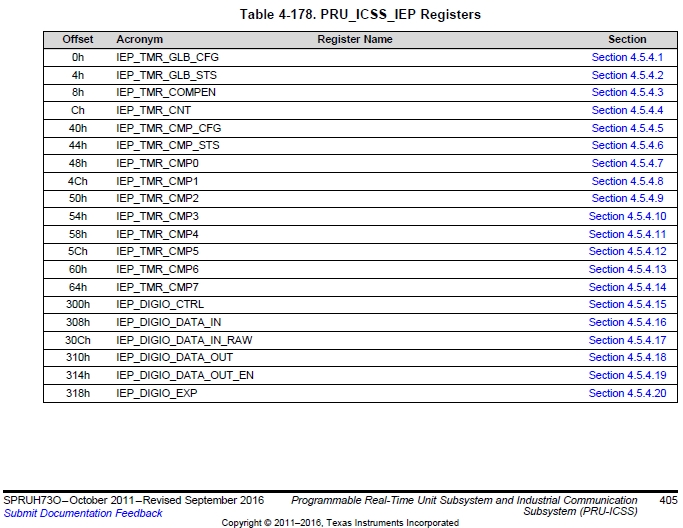

Can someone from TI get the exact value for the following definition constants and variables (using an AM3357):

- CSL_ICSSIEP_CAP_CFG_REG

- ((PRUICSS_HwAttrs *)(pruIcssHandle->hwAttrs))->prussIepRegBase

This constant is used in the following code part of the PRU-ICSS-EtherCAT Slave package:

void bsp_pdi_latch0_control(PRUICSS_Handle pruIcssHandle, Uint8 val)

{

Uint32 reg_val = HWREG(((PRUICSS_HwAttrs *)(

pruIcssHandle->hwAttrs))->prussIepRegBase +

CSL_ICSSIEP_CAP_CFG_REG);

if(val & 0x1) //Latch0 Pos Edge single shot

{

reg_val |= 0x40;

}

else

{

reg_val &= ~0x40;

}

if(val & 0x2) //Latch0 Neg Edge single shot

{

reg_val |= 0x80;

}

else

{

reg_val &= ~0x80;

}

HWREG(((PRUICSS_HwAttrs *)(pruIcssHandle->hwAttrs))->prussIepRegBase +

CSL_ICSSIEP_CAP_CFG_REG) = reg_val;

}

I can't find the values in the package.

Regard,

Patrick