Tool/software: Linux

Hi,

Our customer try to display an image in display using vout1.

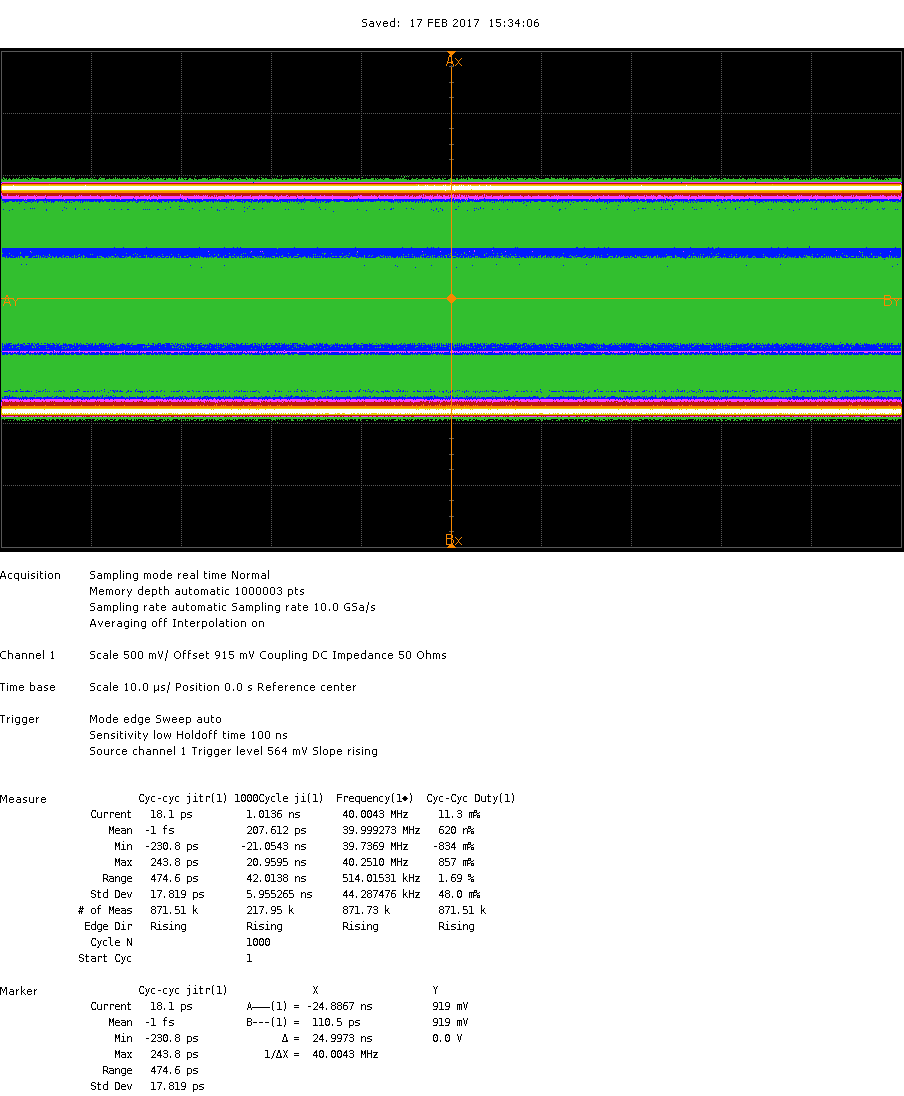

However, the phenomenon that an image displayed by display slips off occurs.

It is observed that the jitter of the pixel clock of vout1 is big.

As a result of having investigated it, it is thought that I may be i886 of eratta.

i886:FPDLink PLL Unlocks With Certain SoC PLL M/N Values

GUIDELINE includes a mention to change the value of PLL.

video1_pll and dispc have the following parameters and did not know it whether jitter decreased when I made which value priority.

Please tell me how I should think as setting to reduce jitter.

①N

②M

③M4

④DISPC_DIVISOR

⑤CM_CLKSEL_VIDEO1_CLK_CLKOUTMUX

The following is set at 40MHz of pclk.

①N=39

②M=1800

③M4=9

④DISPC_DIVISOR=5

⑤CM_CLKSEL_VIDEO1_CLK_CLKOUTMUX=0

Best Regards,

Shigehiro Tsuda