Other Parts Discussed in Thread: INA219

Hi all

I have a design based on the AM5728 eval board. One big difference between the two boards is my board doesn't have a hub on Port 1; it just ties directly to a USB micro jack. We're running the Linux OS based (I think) on SDK version 3. Just using lsusb -t, we can see USB2 devices enumerating on the port just fine, but when a colleague plugs in his USB3 thumb drive, it doesn't detect. A USB3 tester also was not detected when I tried to start characterization testing (I wasn't running the tester; it was run by someone who knows what he's doing).

Is there some set-up in SW that we're missing, something maybe that's needed to tell the port to look for SuperSpeed devices? Is there a write or two I need to do via the debugger?

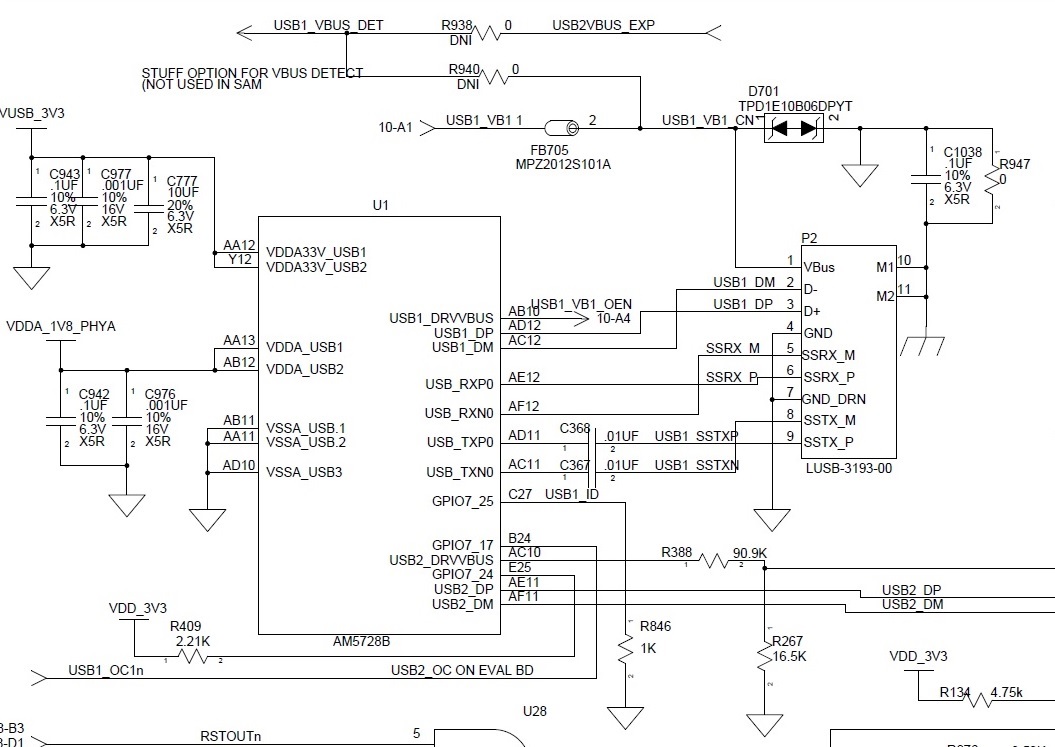

Alternatively, did I miss something in the HW design that's preventing SS detection/links? See schematic screenshot below.

(Apologies, I'm posting this question, then going off the air for a few days, but I will check back as soon as I get back)

Thanks!

MADman