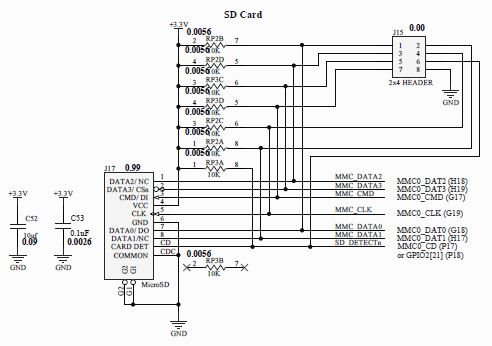

I'm using an AM3351 processor and booting from micro SD card, with TI SDK 3.00. In some cases on startup (perhaps 1 out of 10 tries), the processor fails to detect the bootloader on my SD card (MMC0) and returns the UART output CCCCCCCC. This problem can quickly be circumvented with another power cycle, but this solution will be problematic for our eventual application.

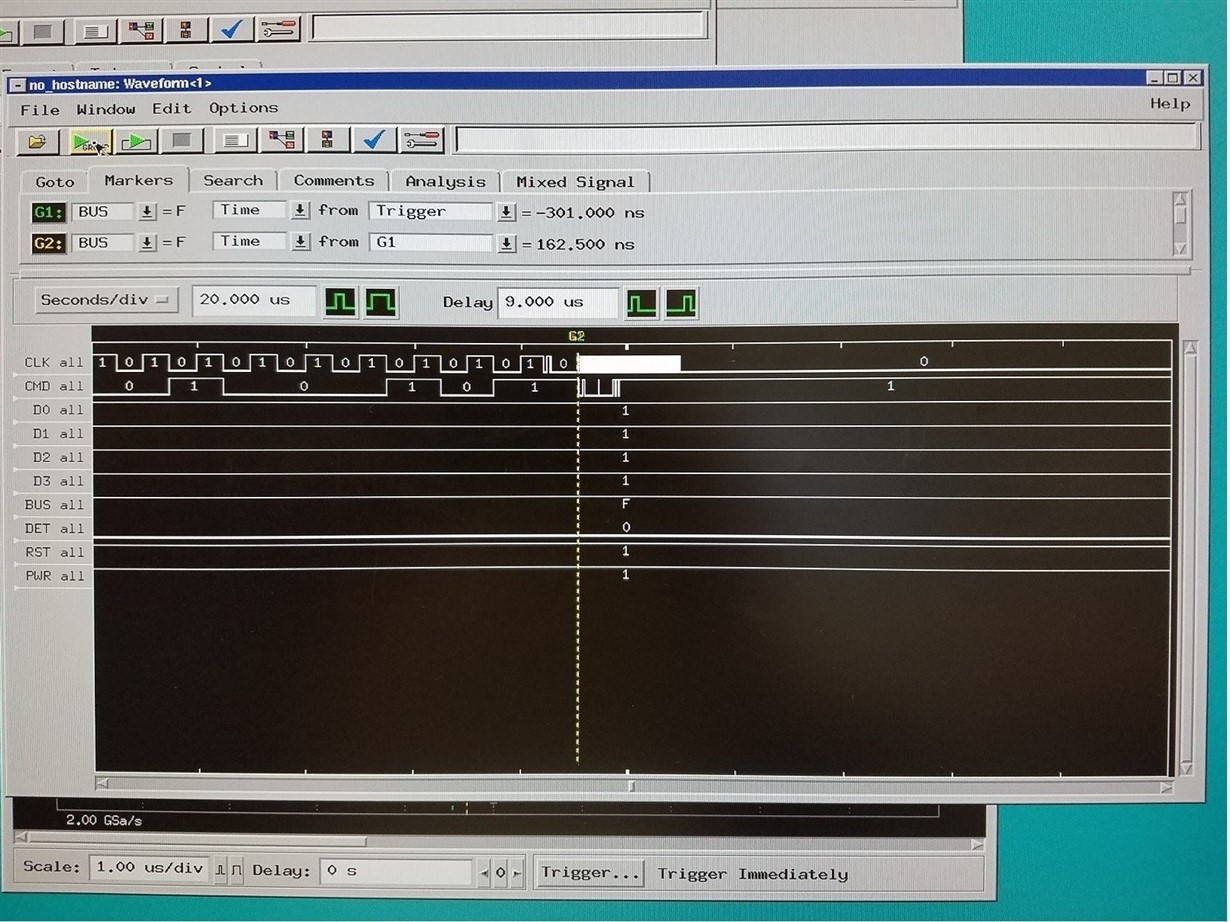

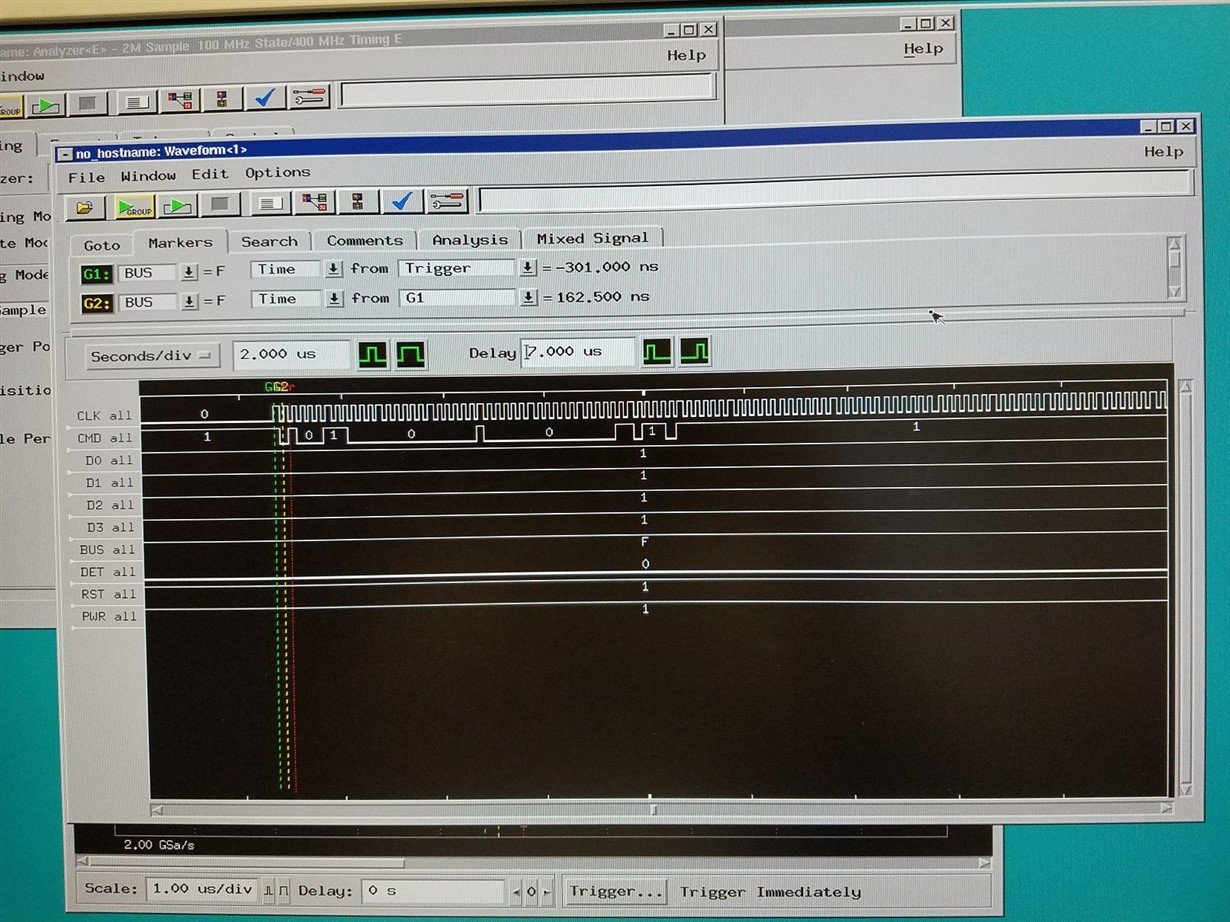

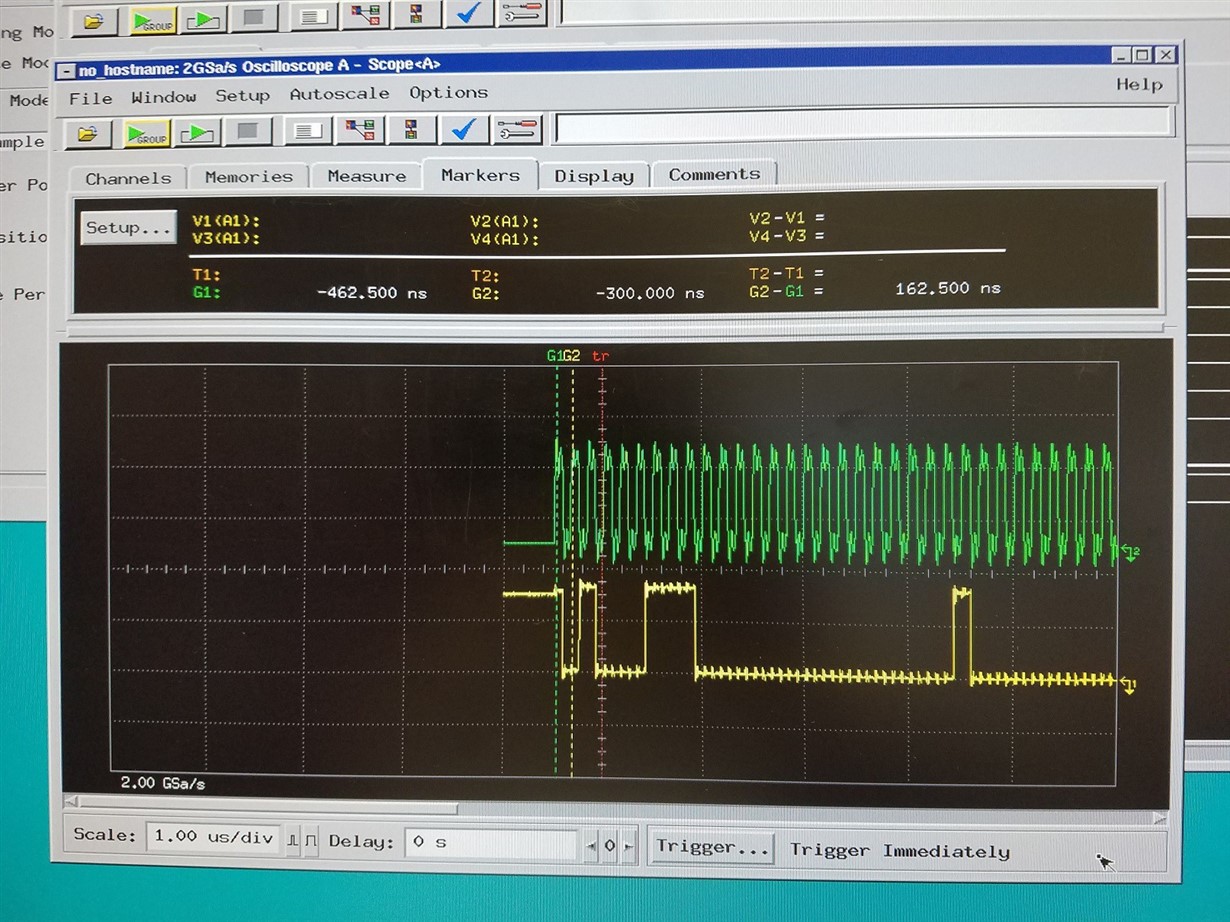

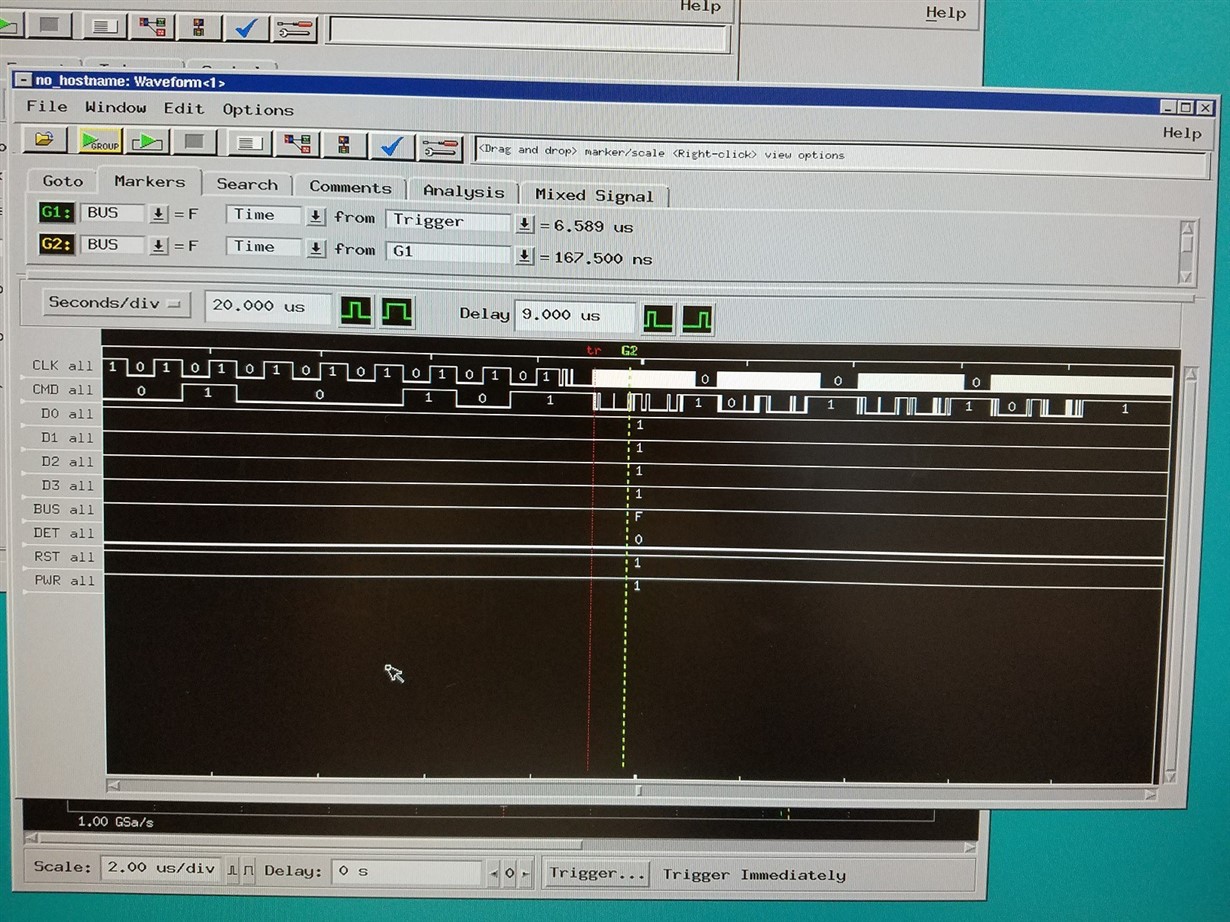

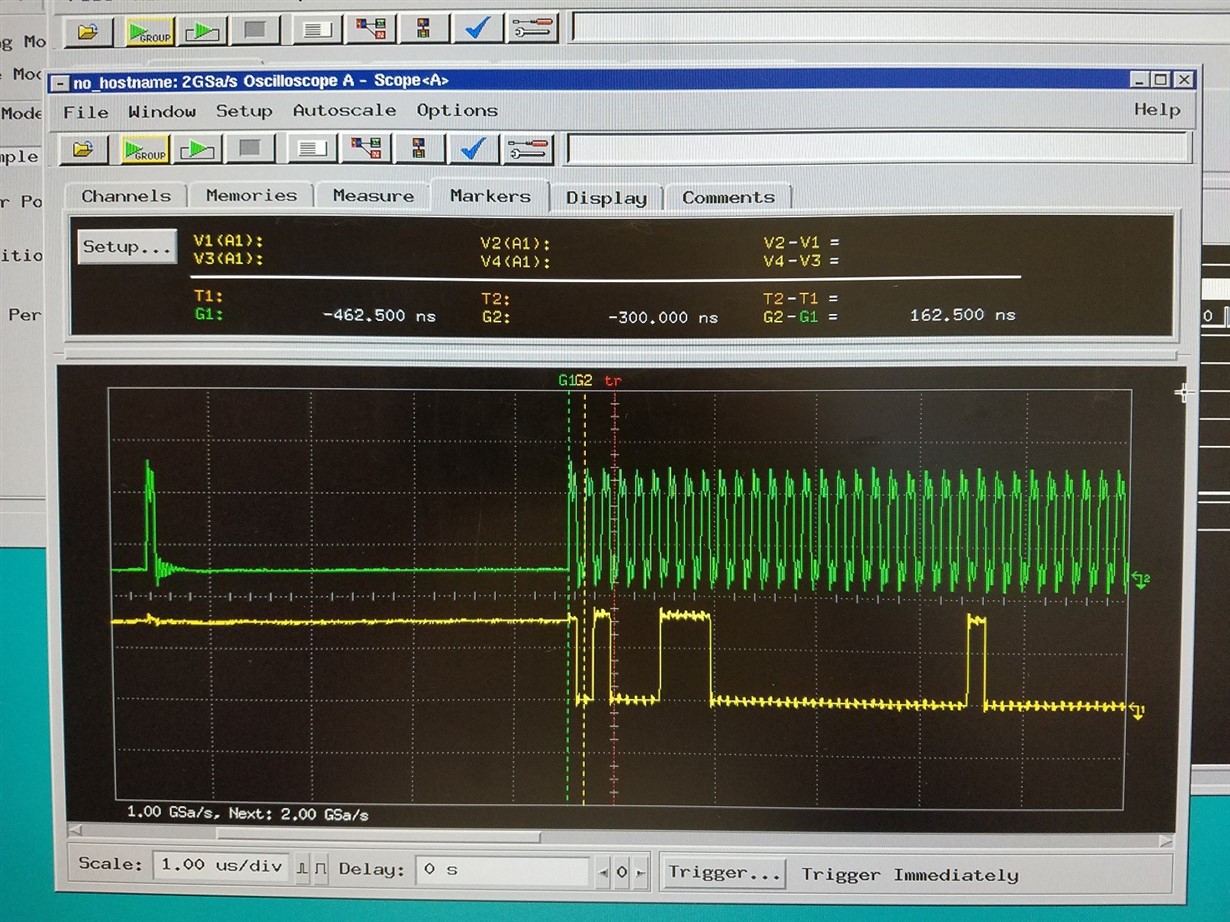

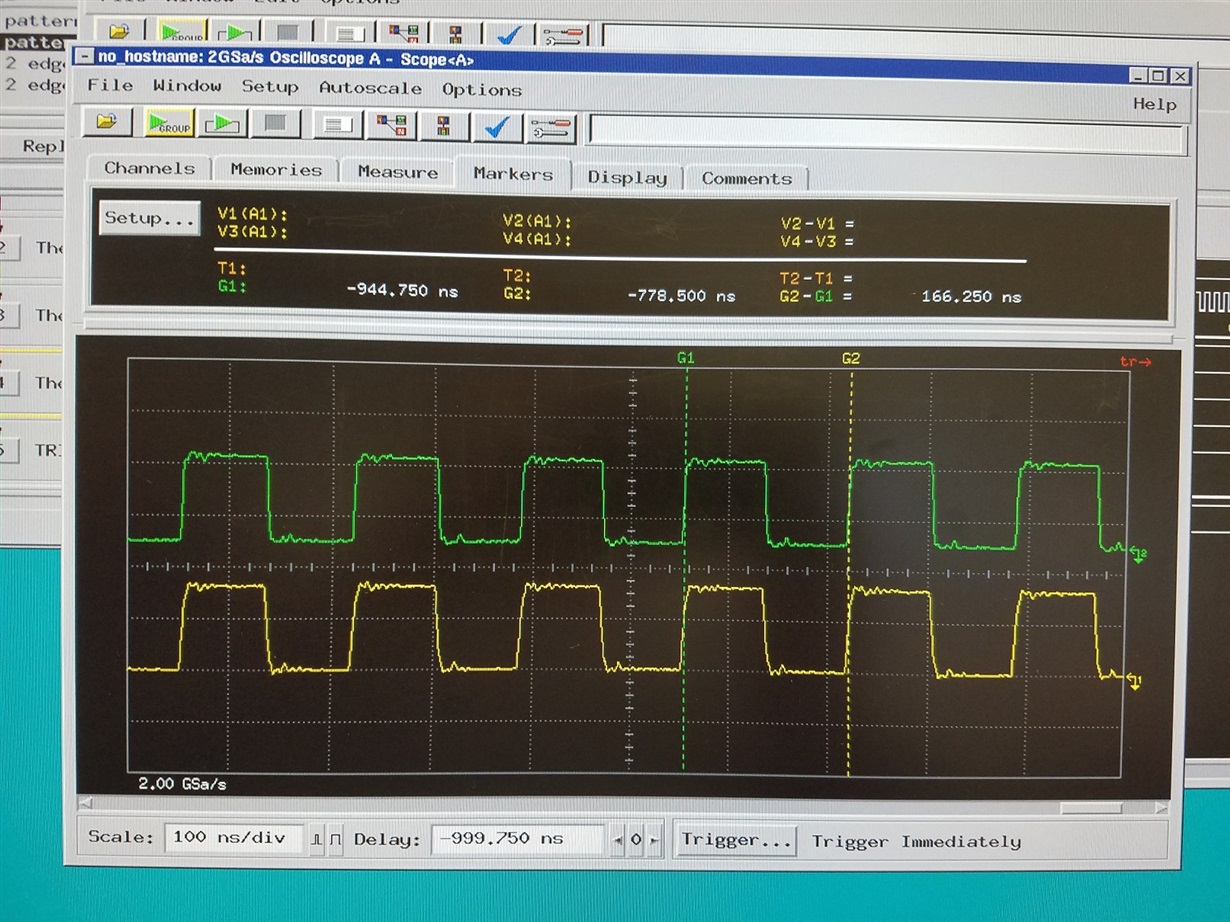

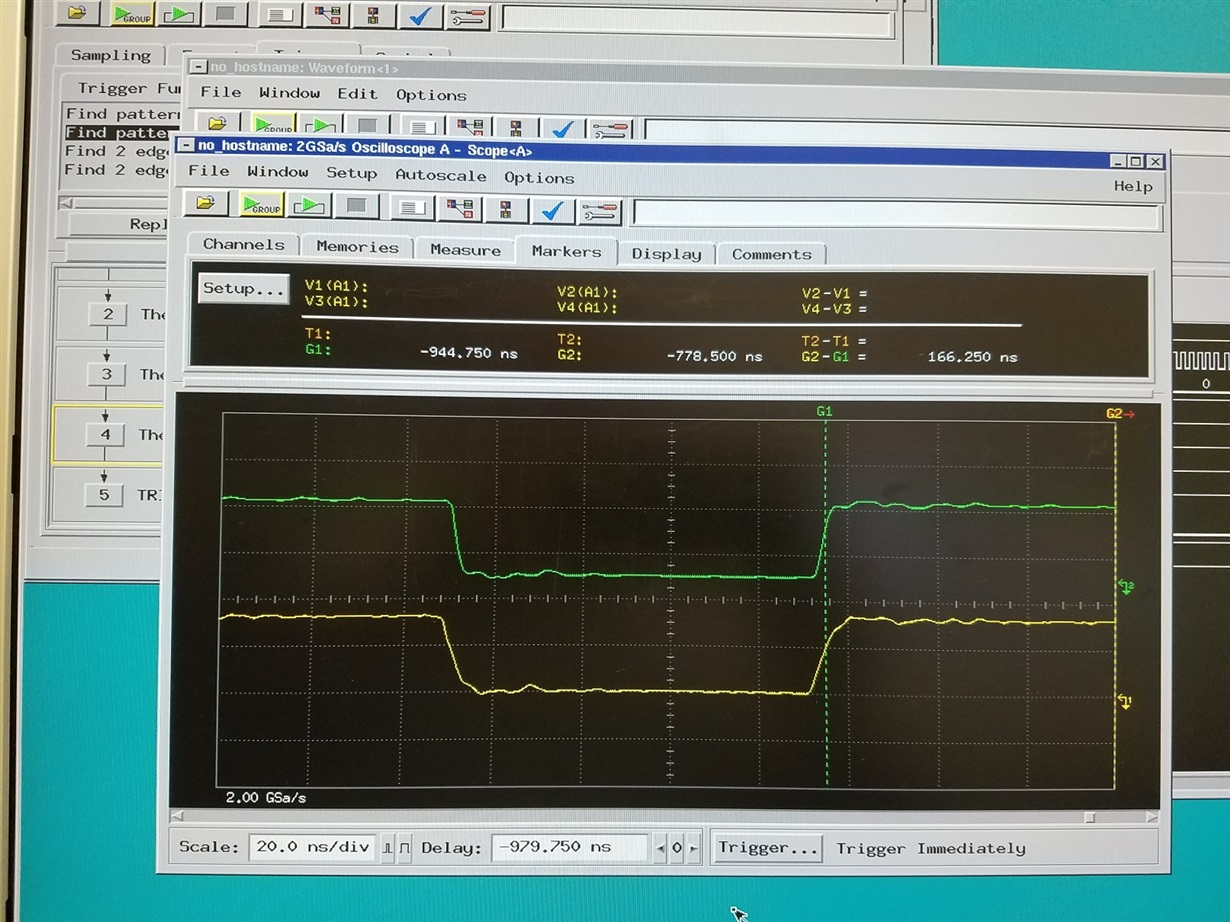

Looking at the MMC0 CMD signal and CLK lines on a scope, it appears to fail when transitioning from low speed to high speed data communication. In both good and bad startup cases, I see command CMD4 or SET_DSR followed by the bytes 04, 04, 00, 00. This is the last command before transitioning to high speed. Once high speed communication begins, in the cases where it fails to start the CMD line goes high and remains high.

Has anyone experienced a similar problem trying to run the bootloader from an SD card? I know that in many cases the MLO and u-boot.img files are stored in on-board memory. Please let me know if you have any suggestions.

Best regards,

Chris