Other Parts Discussed in Thread: SYSBIOS

Tool/software: TI-RTOS

Hi,

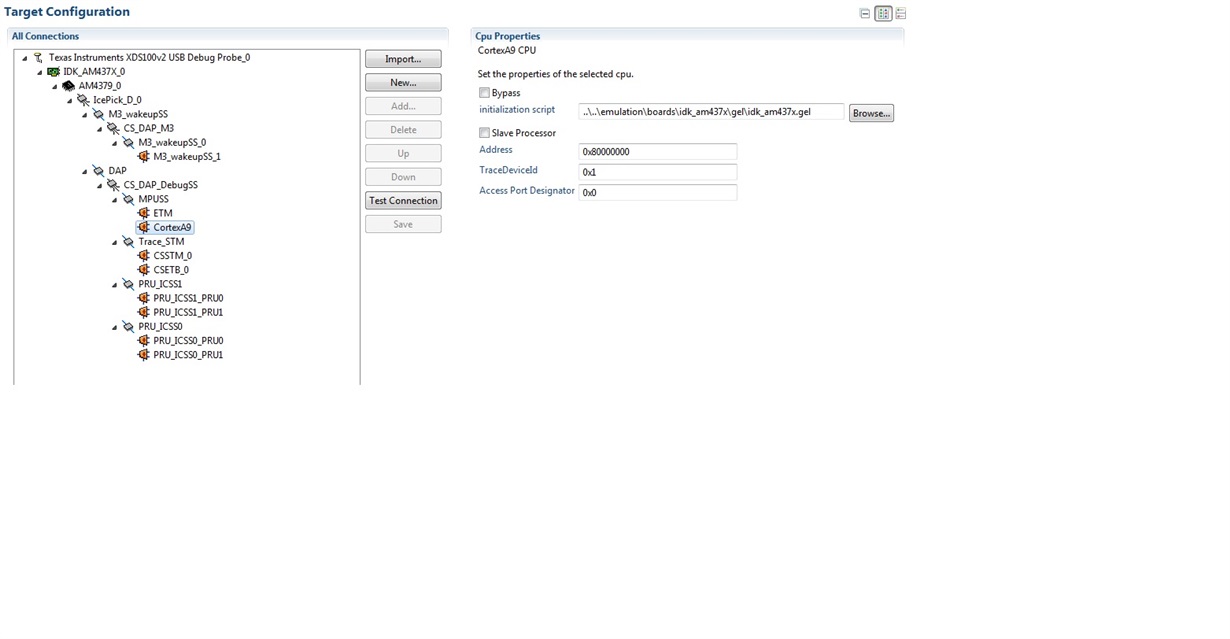

I'm working on PRP example app with processor_sdk_rtos_am437x_3_03_00_04 on idkAM437x.

Application after initialization fail with :

Exception occurred in ThreadType_Task.

Task handle: 0x80132bc0.

Task stack base: 0x80132c10.

Task stack size: 0x2000.

R0 = 0x80134554 R8 = 0x80123e00

R1 = 0x00000000 R9 = 0xffffffff

R2 = 0x54402000 R10 = 0x80123e70

R3 = 0x54403e94 R11 = 0x00000003

R4 = 0xffffffff R12 = 0x80124088

R5 = 0xffffffff SP(R13) = 0x8004e314

R6 = 0xffffffff LR(R14) = 0x80123cf4

R7 = 0xffffffff PC(R15) = 0x80008c98

PSR = 0x80008c98

DFSR = 0x00000005 IFSR = 0x00001004

DFAR = 0x0000000c IFAR = 0xbbb9b7e8

ti.sysbios.family.arm.exc.Exception: line 205: E_dataAbort: pc = 0x80008c98, lr = 0x80123cf4.

xdc.runtime.Error.raise: terminating execution

Aplication is build with Debug option.

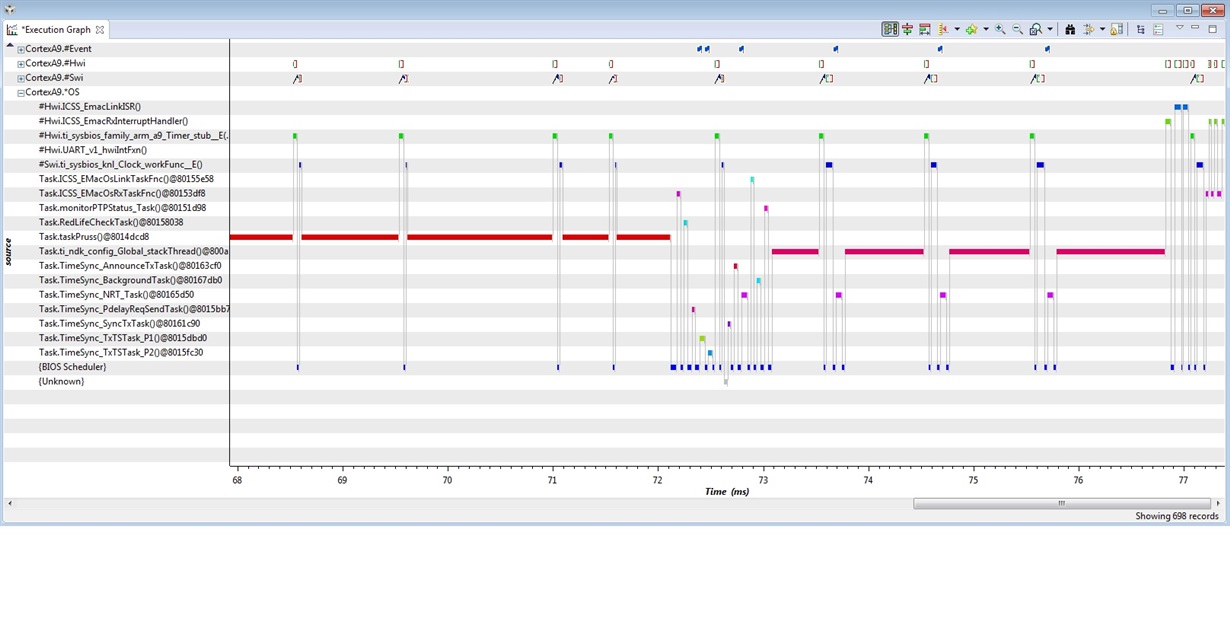

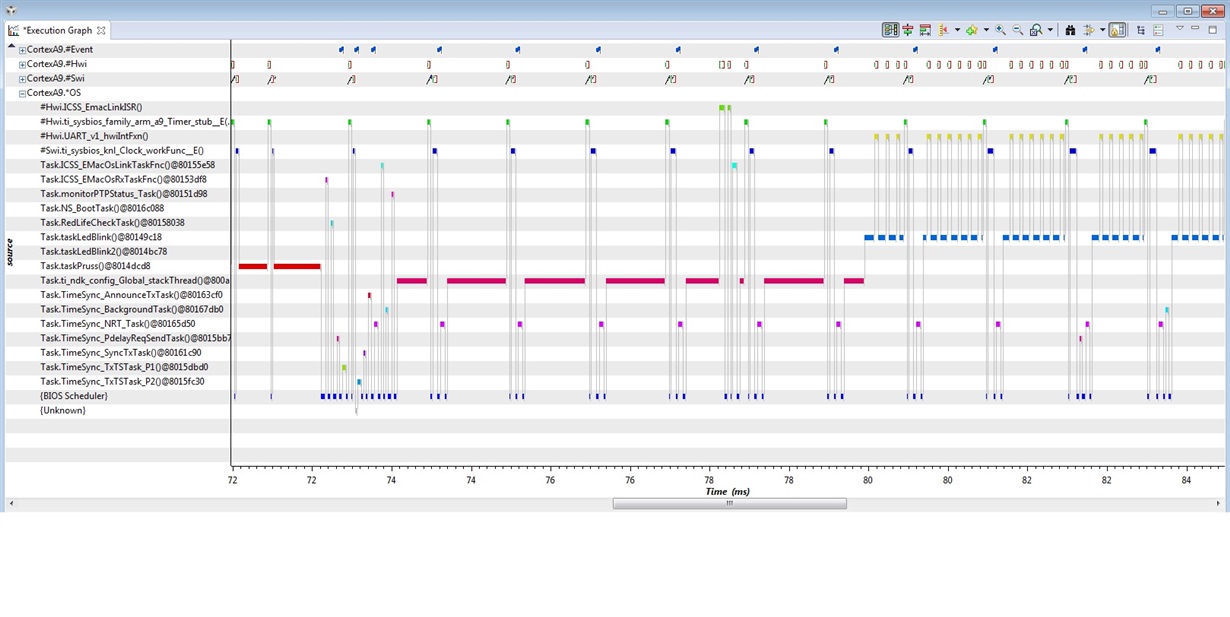

As far I succeeded with step debugging, it look like something go wrong in NC_NetStart function. (stack: ti_ndk_config_Global_stackThread -> NC_NetStart)

I'm surprised with problem because is "original" app provided from TI.

What should be reason?

Best Regards,

Mare