Other Parts Discussed in Thread: TMDXSK437X

Hello,

I have seen the noise on DDR_A0 (N1) line in TMDXSK437X.

Since its noise also can be seen in our target board, we think AM437x output the noise.

a) AM437x DDR controller potentially output noise on A0 line. Is it known issue ?

b) We encounterd read/write error on our target board. To avoid it we are considering to change the termination resistor value from 50ohm to 100ohm.

Do you think its workaround have any possible to encounter any another problem?

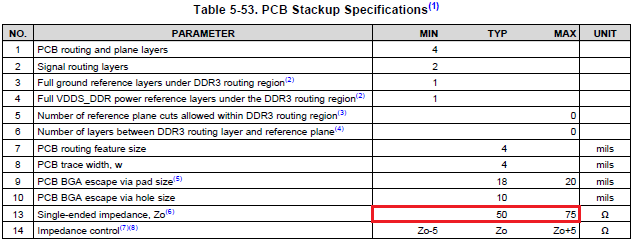

Because datasheet specifies Zo as typ 50ohm max 75ohm.

c) Can you recommend the DDR3L design without termination regulator? It's another our workaround to avoid read/write error.

Best regards, RY

DDR_A0 (N1) line noise n TMDXSK437X

AM437x datasheet specifies Zo as typ 50ohm max 75ohm