Hello,

I am trying to generate a interrupt from Mailbox1 to DSP1 on AM572X board, but the IFR doesn't change and my ISR doesn't be invoked when I push a message into MAILBOX1 by using command "devmem 0x4A0F4040 w 0x12345678" on CA15

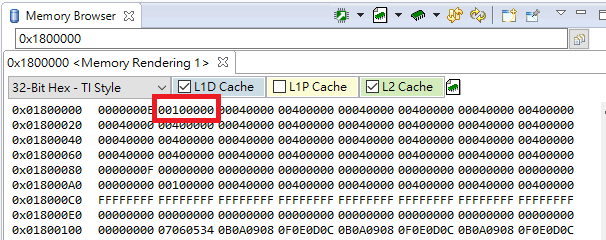

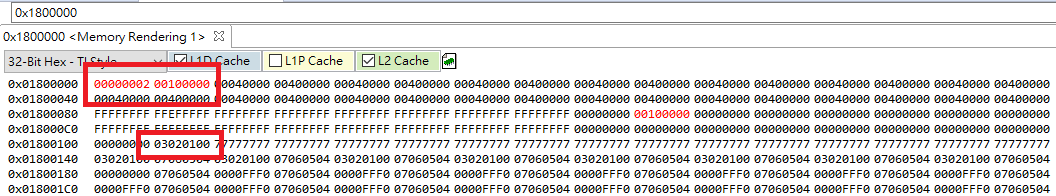

I am sure that a interrupt is generated from MAILBOX1 (by checking MAILBOX_IRQSTATUS_CLR_u (0x4A0F0008)) and the C66X CorePac interrupt event NO. 52 bit is set (by checking interrupt event flag register (0x1800004)).

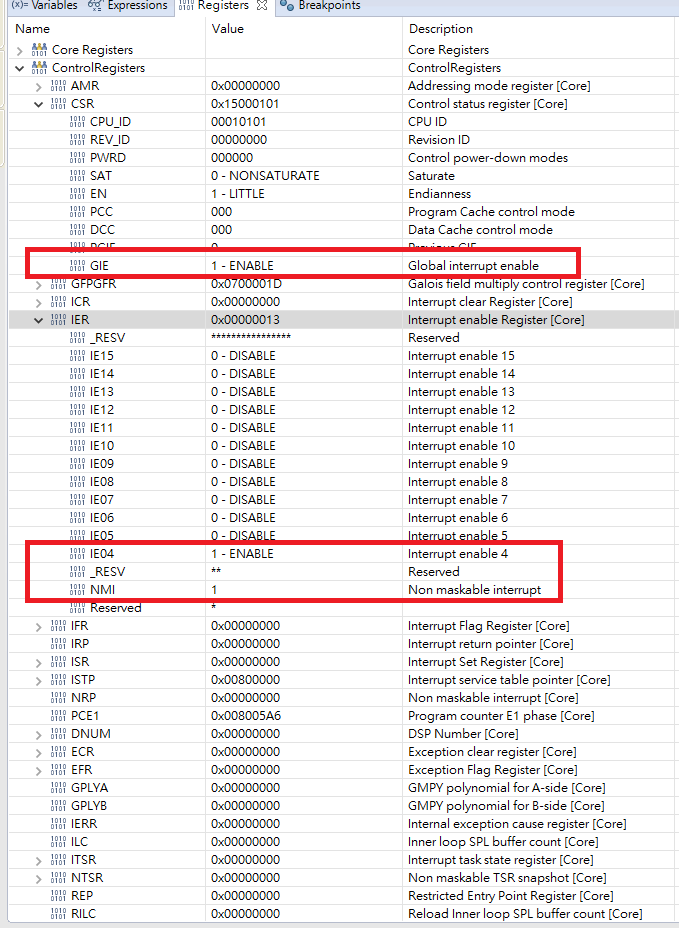

I have configured the following registers to map MAILBOX1_IRQ_USER0 to the CPUINT4 of DSP1.

- CRS.GIE = 1

- IER.IE4 = 1

- IER.NMI = 1

- INTMUX1.INTSEL4 = 52

- CTRL_CORE_DSP1_IRQ_52_53[8:0] = 21 (by default)

- MAILBOX_IRQENABLE = 0x05050505

Please give some suggestion!

Thanks,

Hungwei

The control registers are shown as follows.

The interrupt event flag register is shown as follows