Tool/software: Linux

I'm working with an am3358 running linux kernel 4.9.69. Our board has a few Nordic radios connected as SPI slaves to the am3358. We operate the SPI bus at 8MHz. All of our SPI transactions are pretty small: less than or equal to 64 bytes, but there are a lot of them.

Everything works flawlessly when DMA is not involved, although we are seeing pretty high CPU usage. The system has run flawlessly for more than a week.

Recently I've started looking into using DMA for the SPI transactions to try to reduce the CPU load. The driver spi-omap2-mcspi.c uses the following to decide whether or not to use DMA:

#define DMA_MIN_BYTES 160

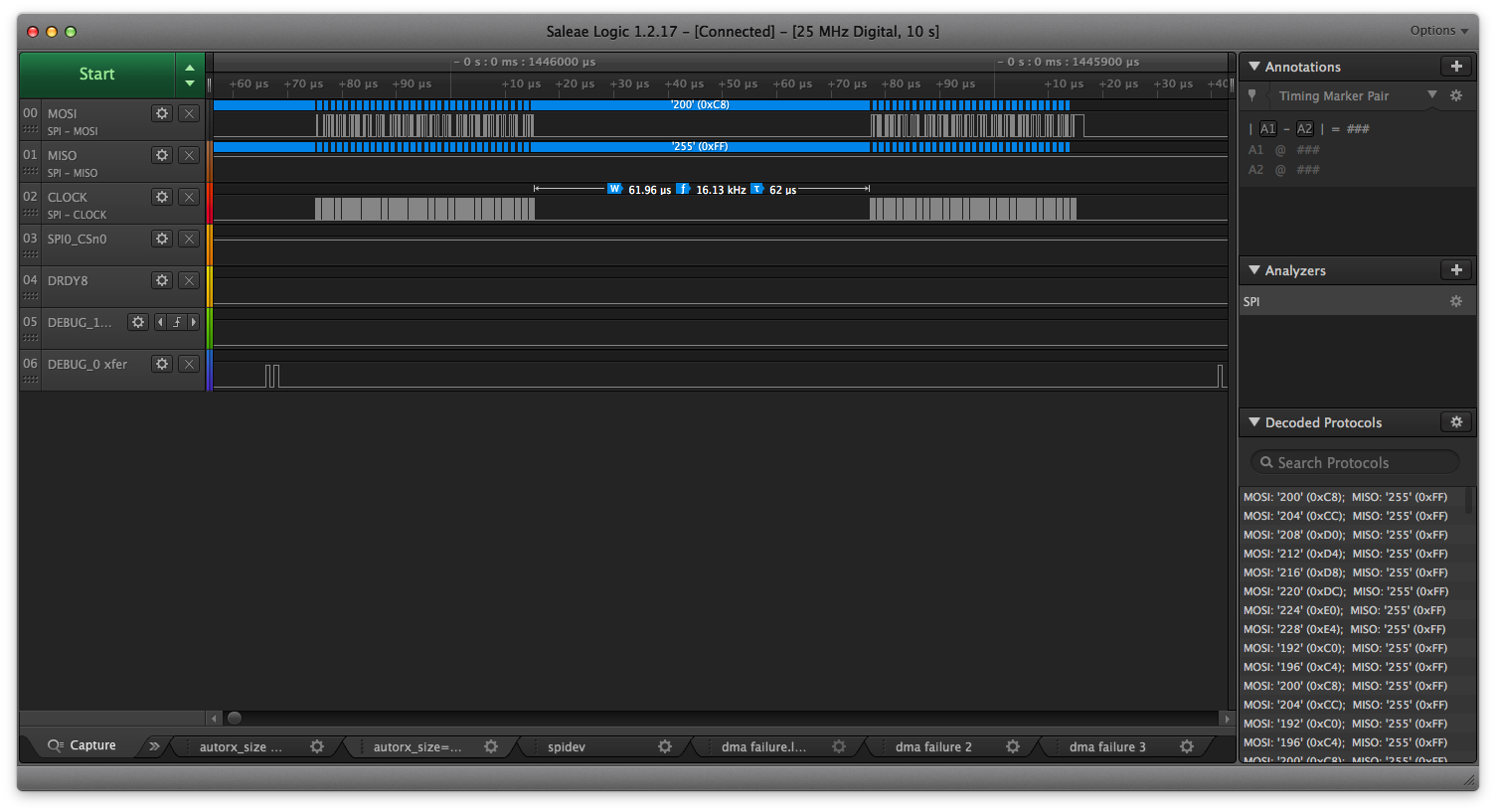

I changed this value to 0, so that the DMA is used for every transaction, and I'm seeing a pretty significant reduction in CPU usage by doing that. However, SPI doesn't work flawlessly anymore. I see the SPI transactions stop after about 1/2 hour to 1 hour. I also see this happen if I set DMA_MIN_BYTES to 32 or 64.

Do you have any idea why that would be? Do you know of any reason enabling DMA on smaller transactions would cause the SPI to stop working? There don't appear to be any errors propagated up to our driver that is using the SPI subsystem. And there aren't any errors I see when I enable debug in spi.c and spi-omap2-mcspi.c

Thanks!