Part Number: BEAGLEBN

Hi,

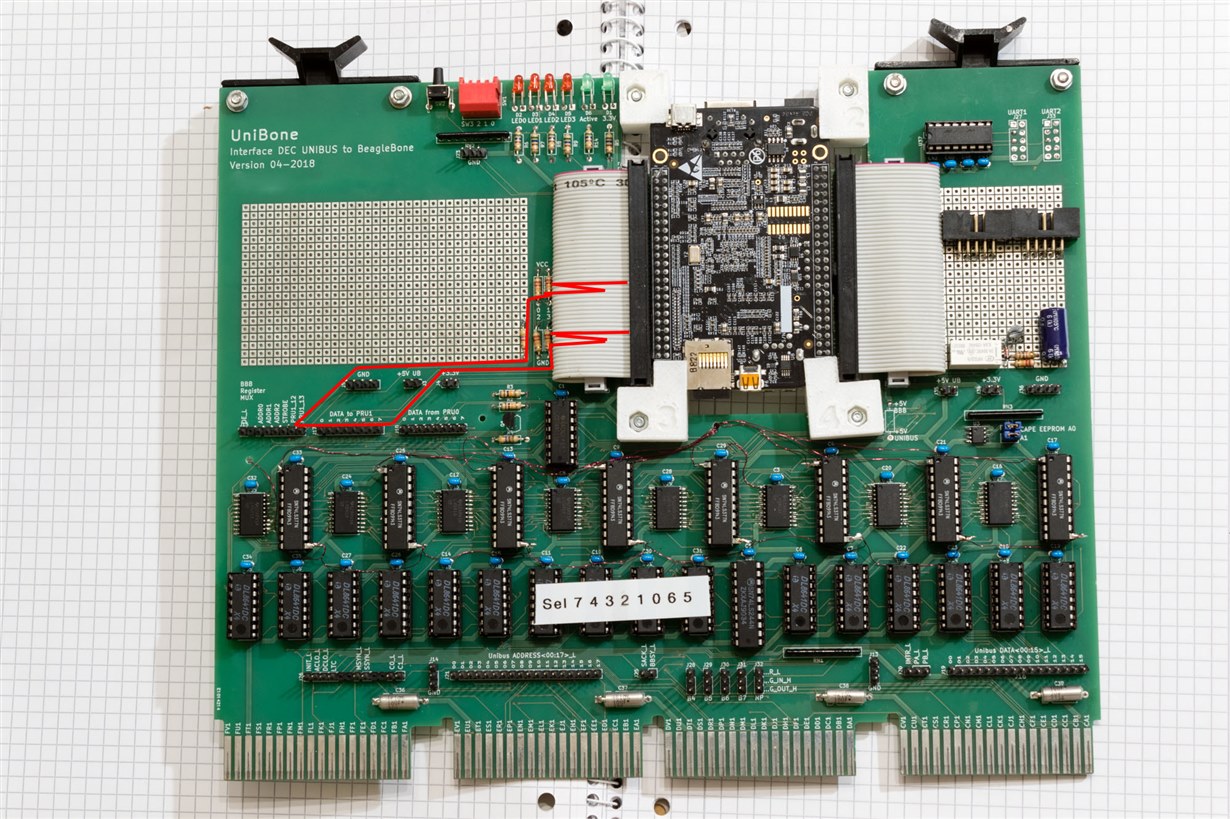

I use the PRUs in a BeagleBone. PRU software is written in clpru 2.2.1.

I can not reach the timing goals for my project.

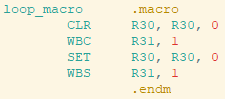

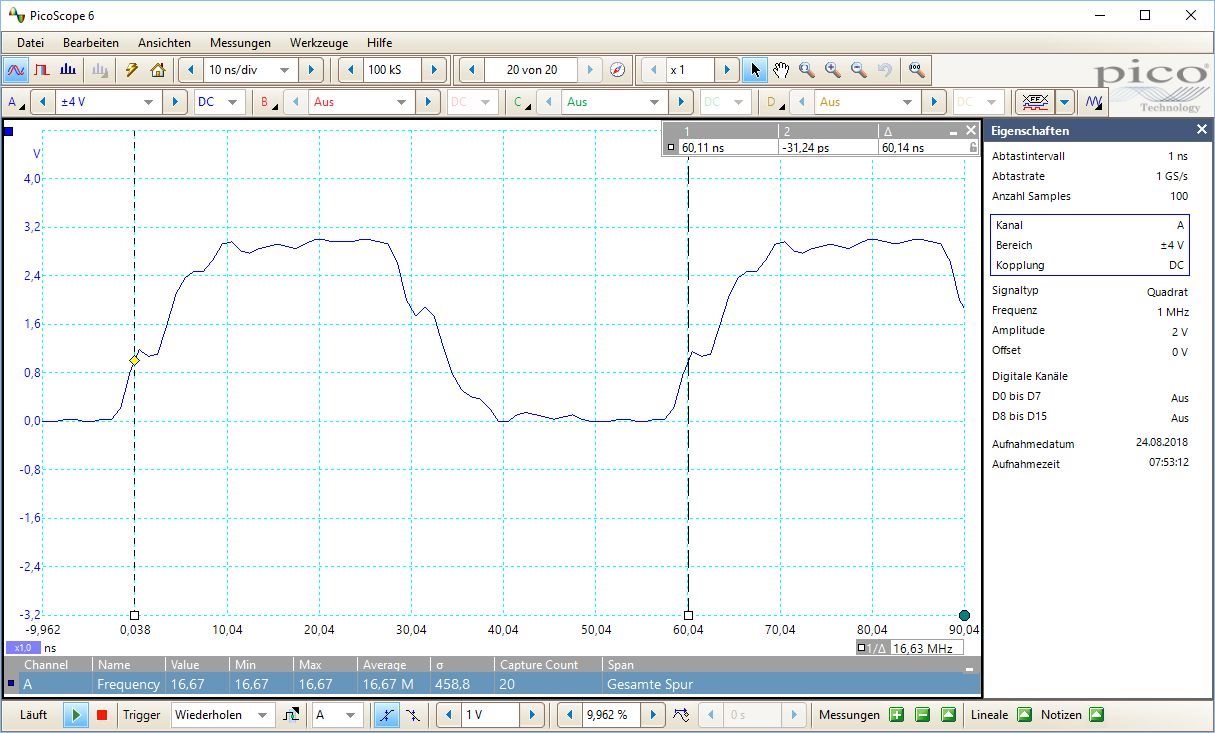

Debugging leads to the result that a simple write-read-back on the GPIOS need 40ns to complete, not 10ns as expected.

Test setup: I toggle an R30 output pin and wait until the voltage level re-appears on R31.

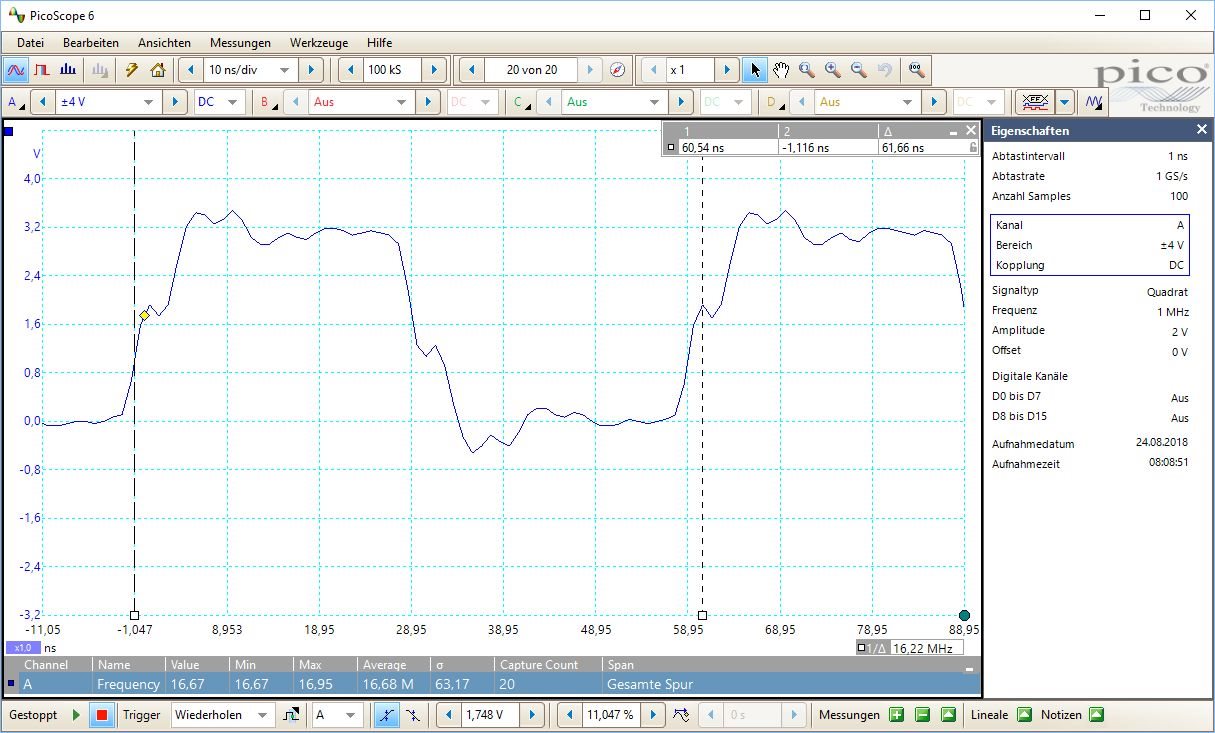

Code:

while (1) {

__R30 |= (1 << 12); // set PRU1.12

while (!(__R31 & 0x80)) ; // wait until readback on DATAIN7

__R30 &= ~(1 << 12); // clear PRU1.12

while (__R31 & 0x80); // wait until readback on DATAIN7

}

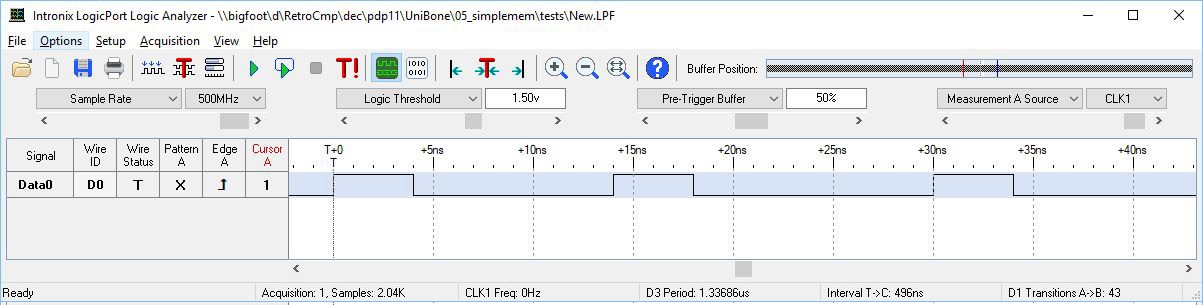

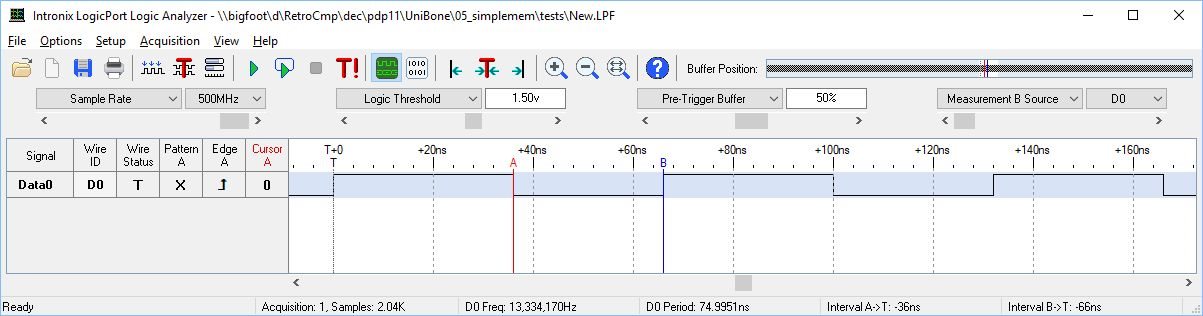

The logic analyzer shows that a single

__R30 |= (1 << 12); // set PRU1.12

while (!(__R31 & 0x80)) ; // wait

needs 40 nano seconds.

I can generate a good square wave at 66MHz with

while(1) {

__R30 |= (1 << 12); // 5ns

__R30 &= ~(1 << 12); // 5ns

}

so the "while (!(__R31 & 0x80)) ;" part needs 35ns.

http://processors.wiki.ti.com/index.php/AM335x_PRU_Read_Latencies says: EGPIO read is 1 cycle = 5ns.

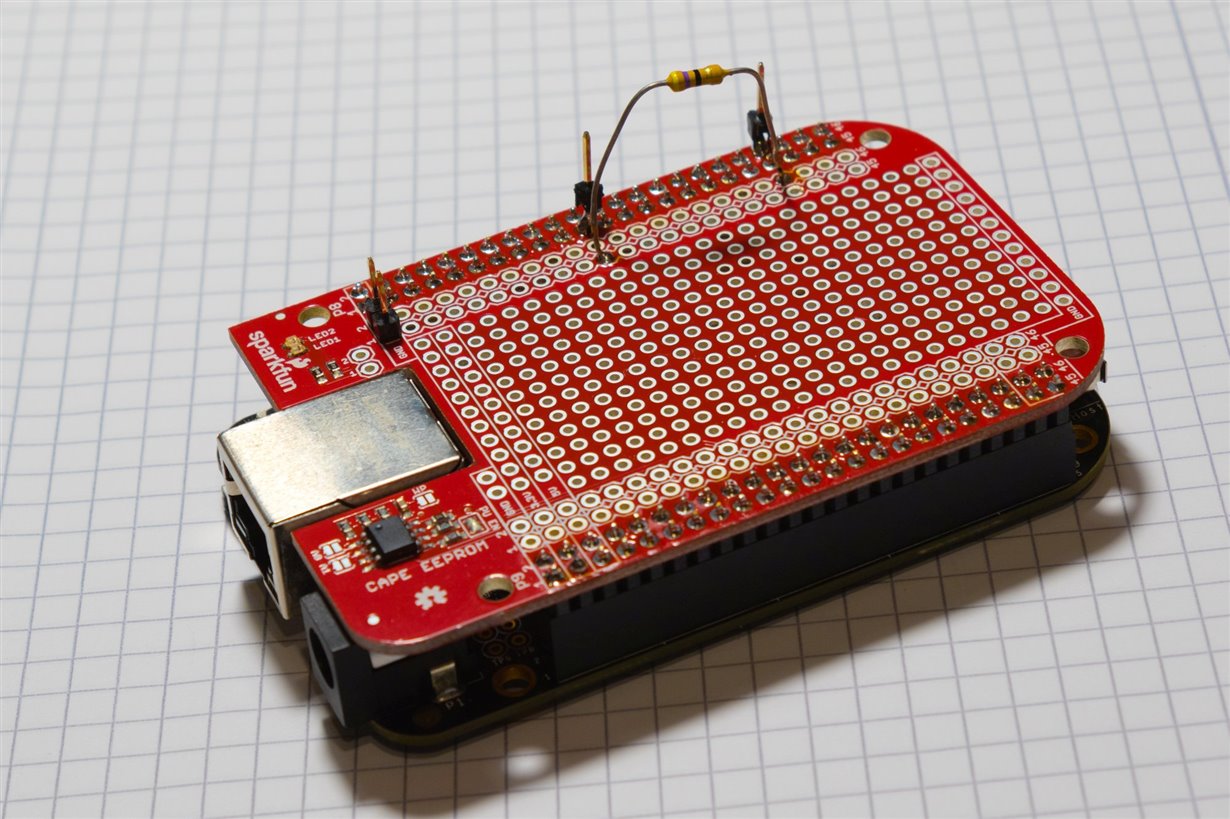

The BeagleBone itself apparently does not contain an low passes.

What could causes a delay of 7 cycles on EGPIO R31 read?

thanks for caring,

Joerg Hoppe, PEAK System Technik GmbH