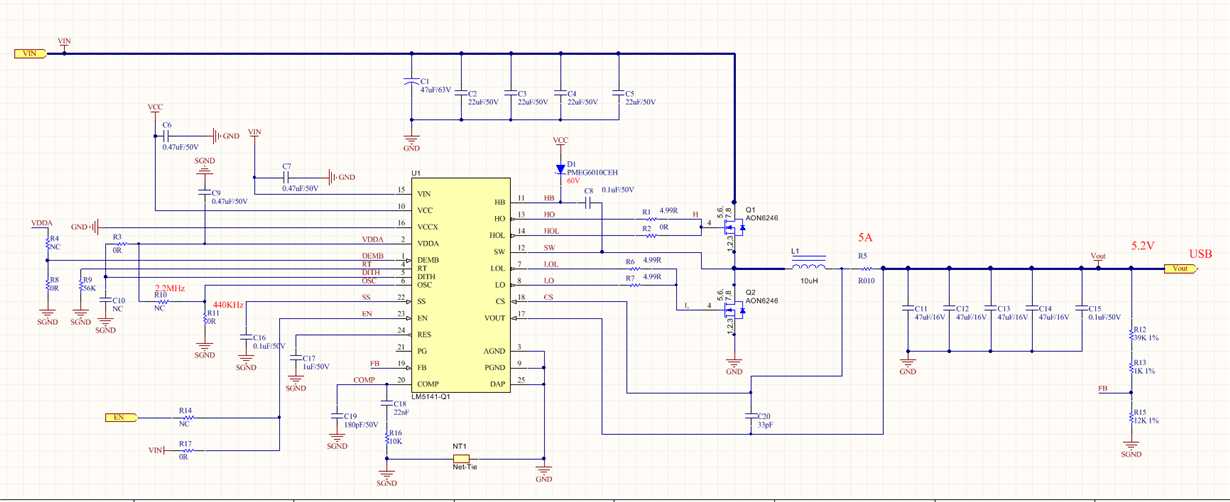

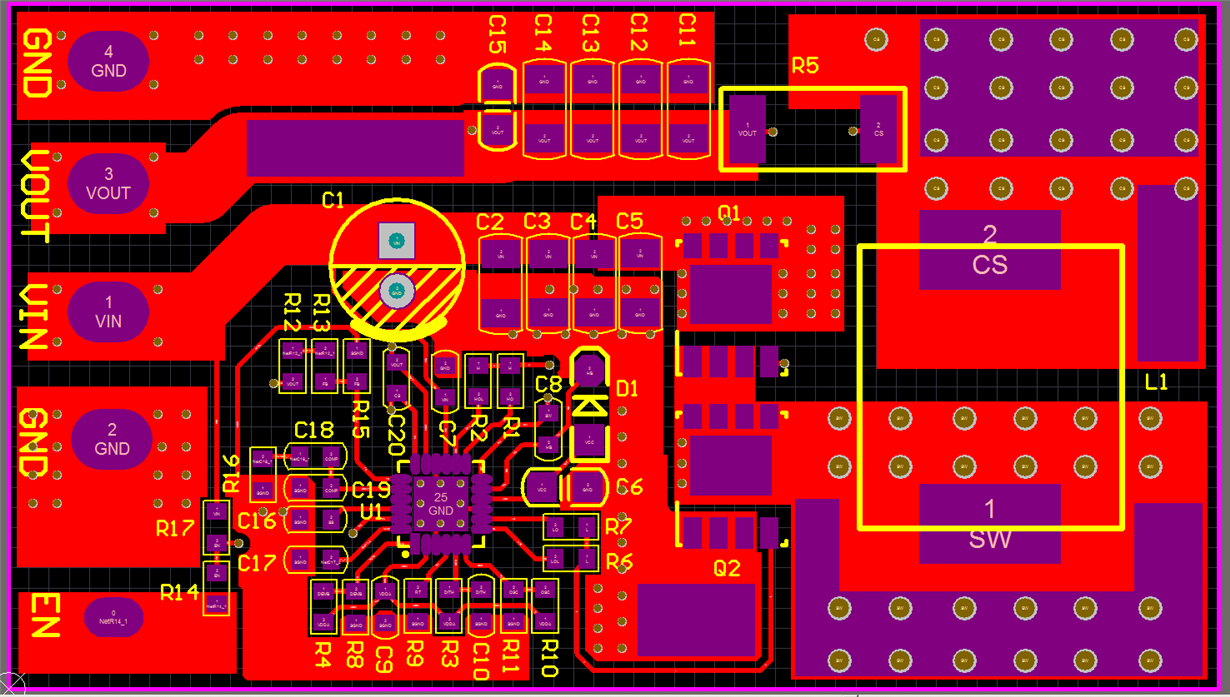

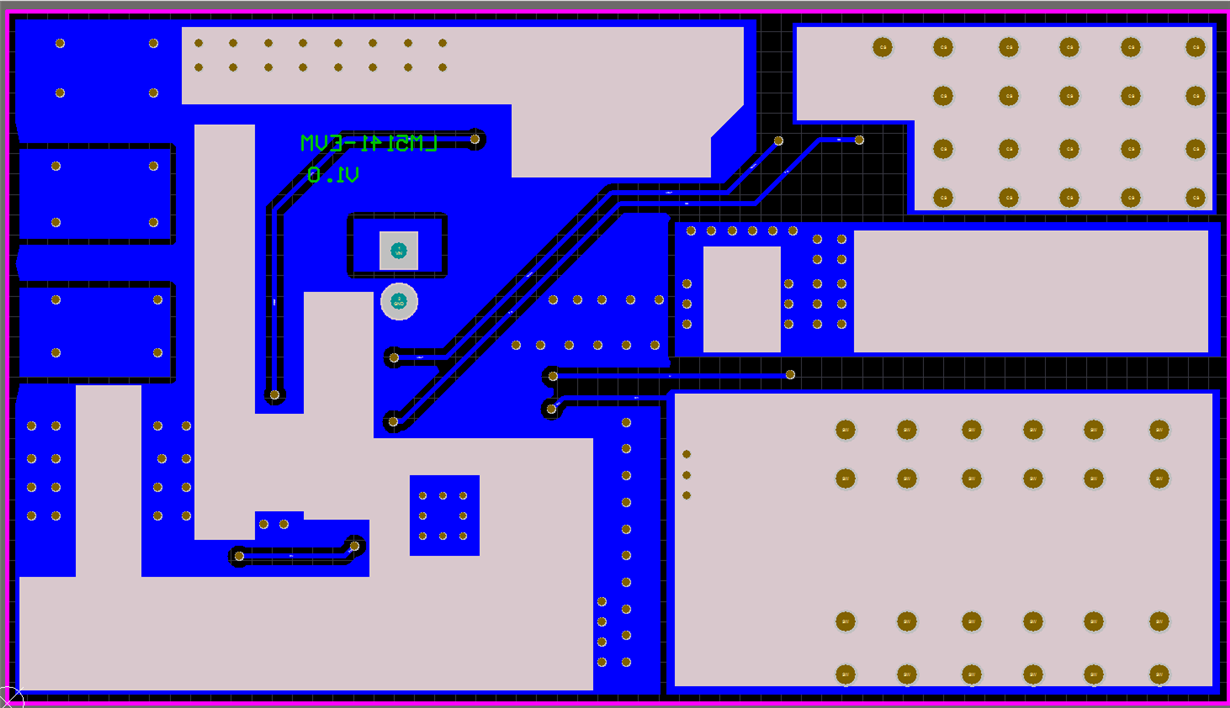

This is my second design LM5141,40V-5.2V DC-DC

I design the EVM refer to the WENBENCH tool schematic

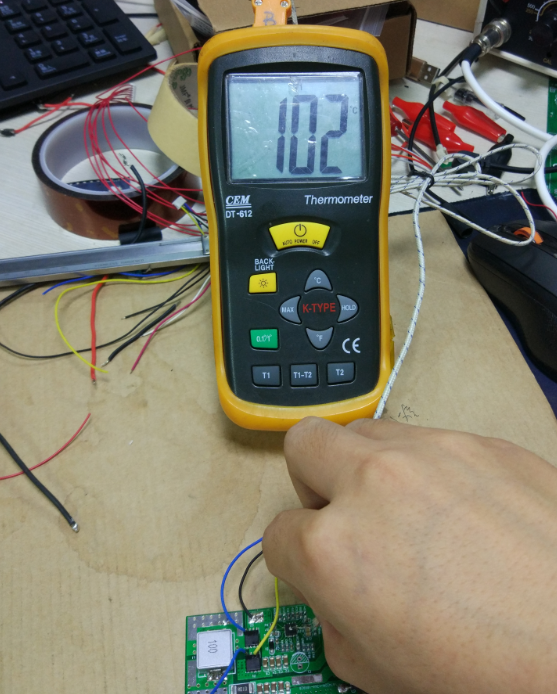

When input is 40V,output is 5.V 3A,IC and MOS are very hot,about 100℃,

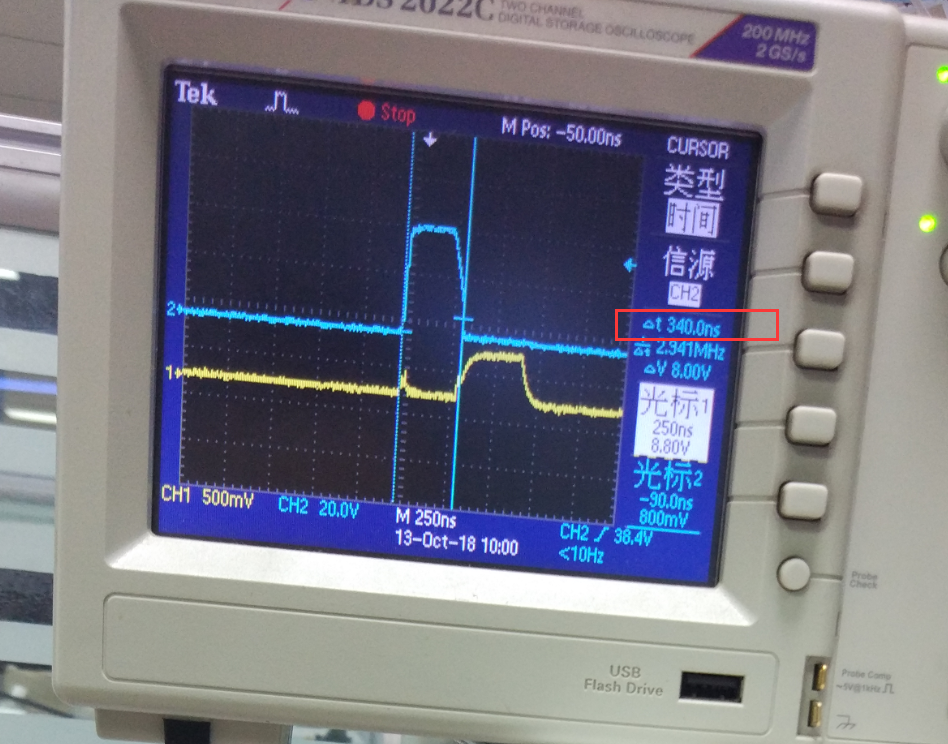

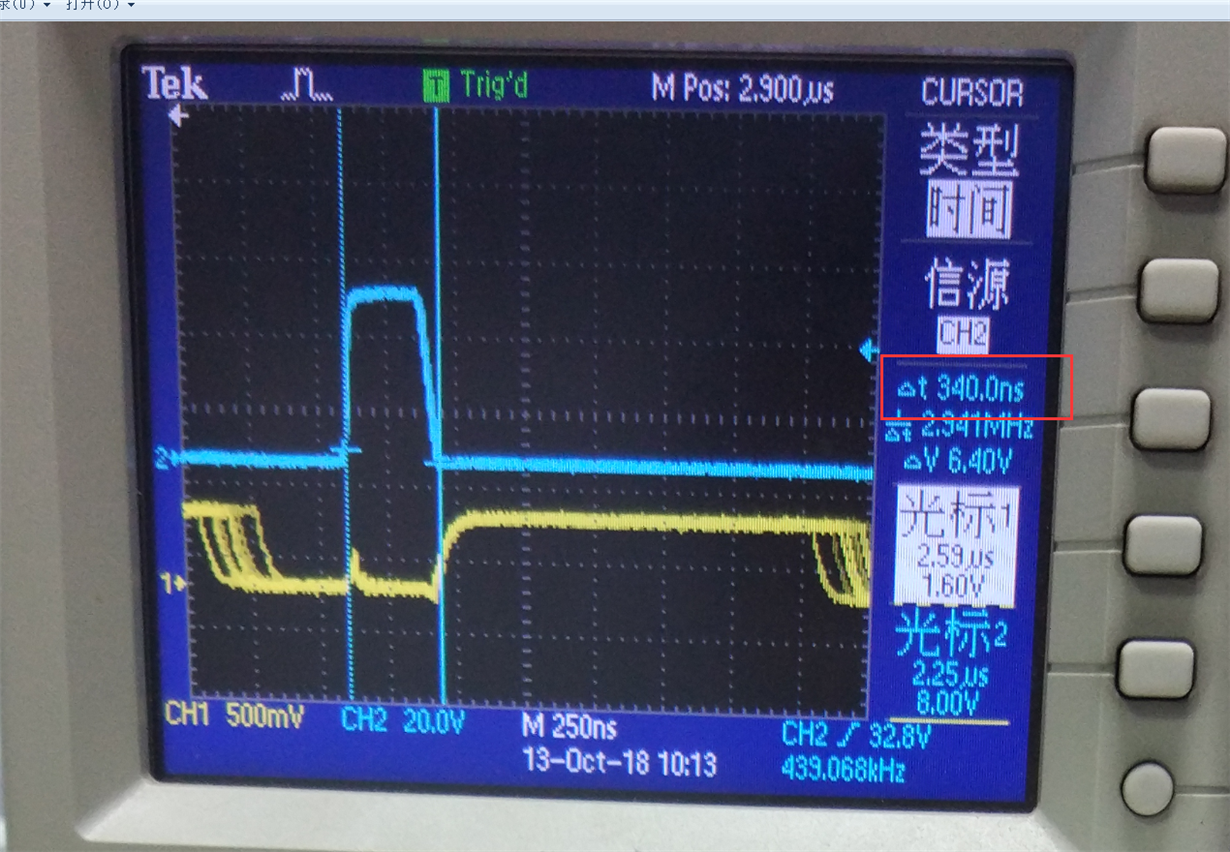

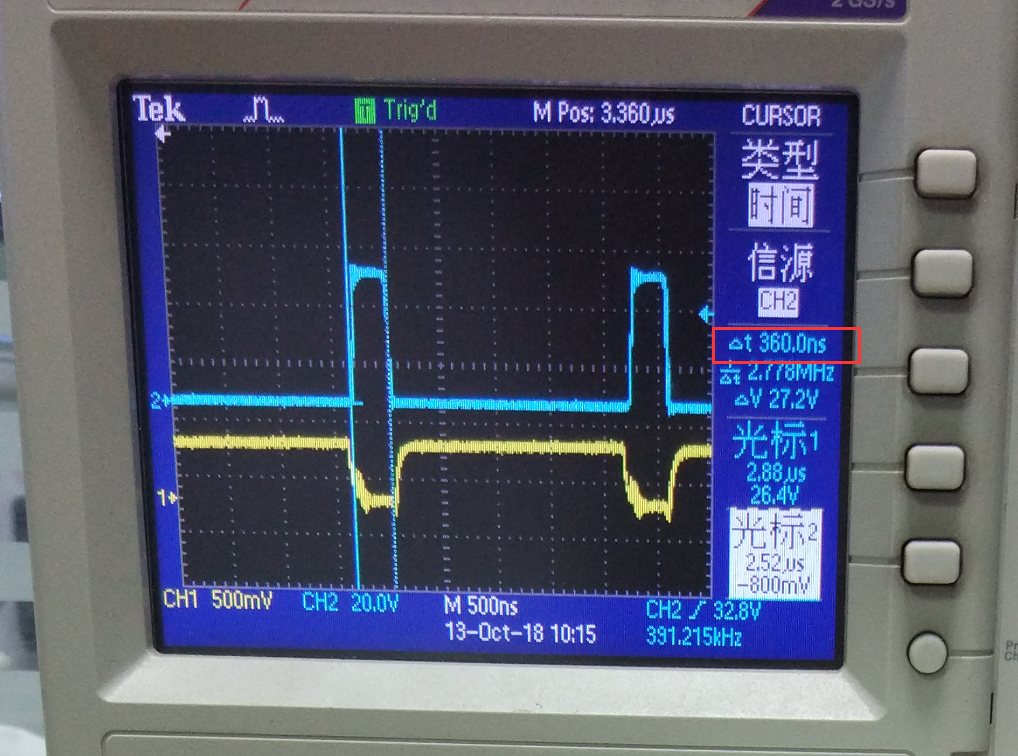

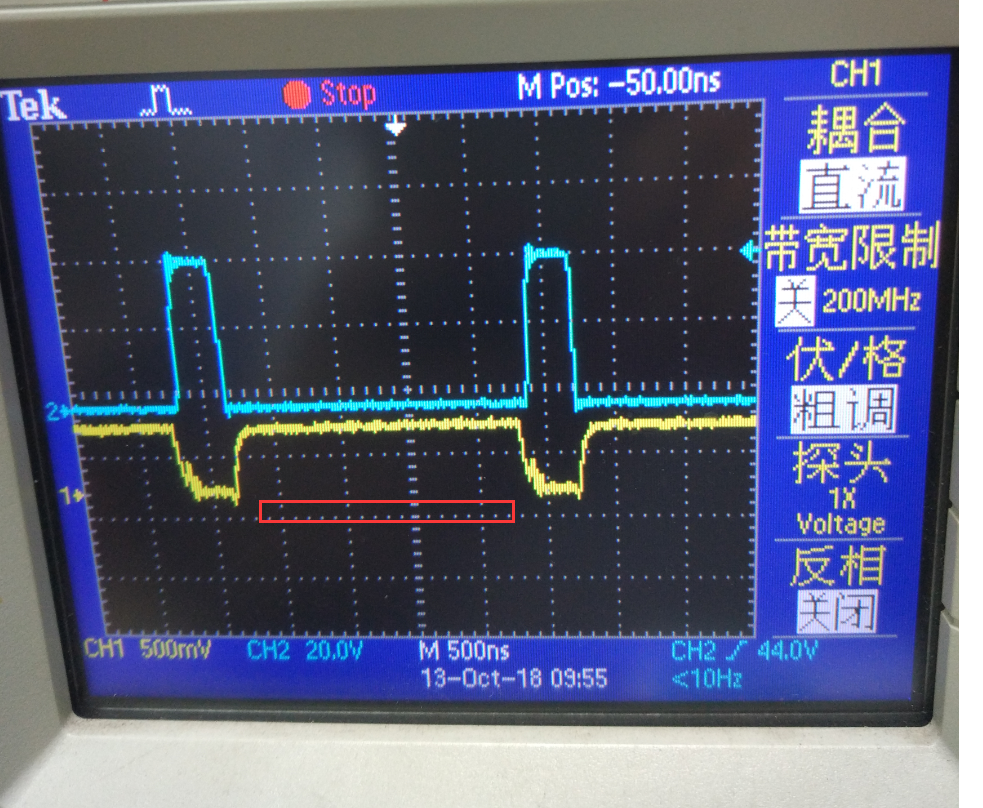

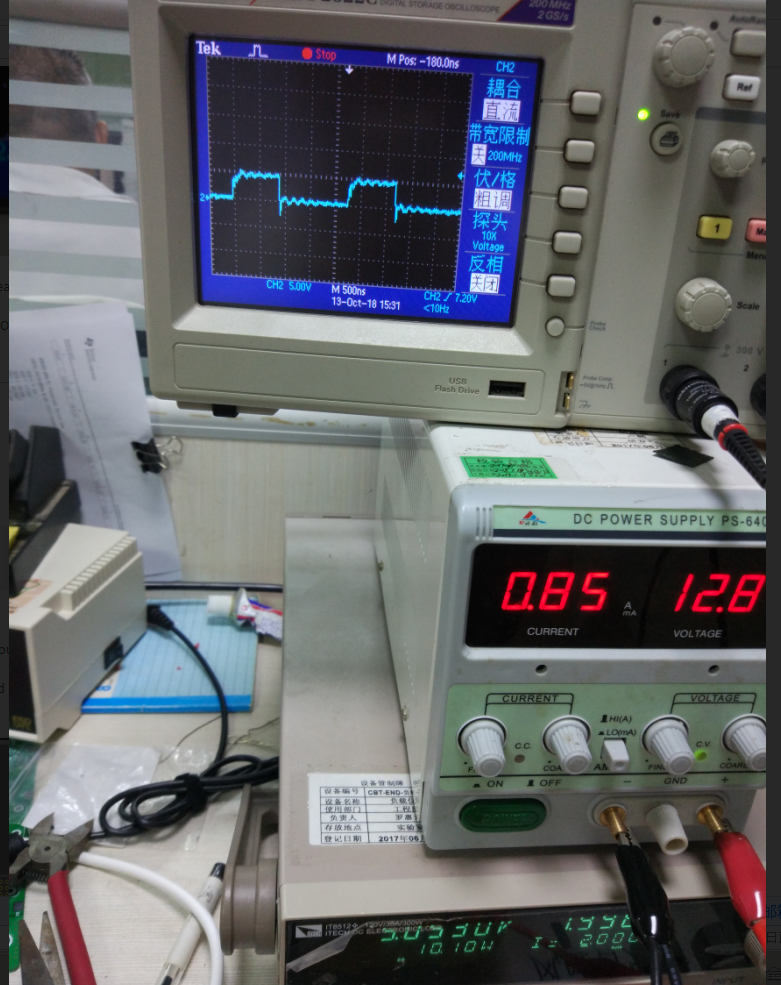

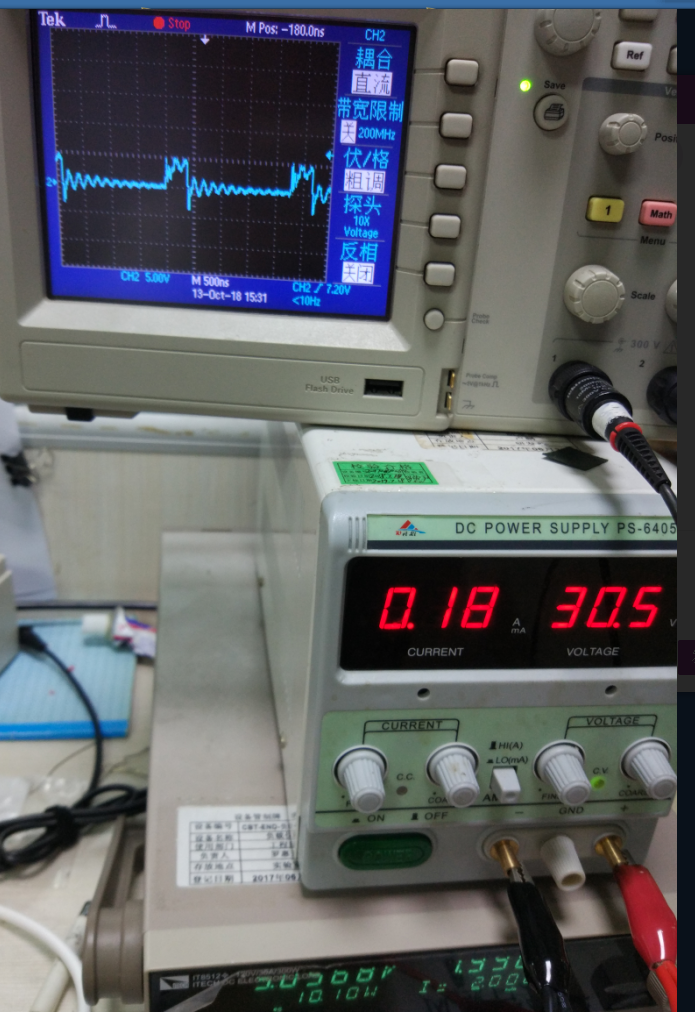

Here are there picture about the high and low MOS driver waves,in different output current。

Blue diagram is high MOS driver

Yellow diagram iS low MOS driver

output is1A

output is 2A

output is3A

See the above there picture,when operate the different output current ,the high MOSFET driver open time almost keep unchanged

Let us see the low MOS diver wave changes in different output current

1A

2A

3A

I am in interrogative ,as usual,when the loading is added,the high driver should gain the duty cycle in the buck circuit,Otherwise this state is not my hope, and why only the low driver duty cycle was added when the output current was added 1A to 3A?

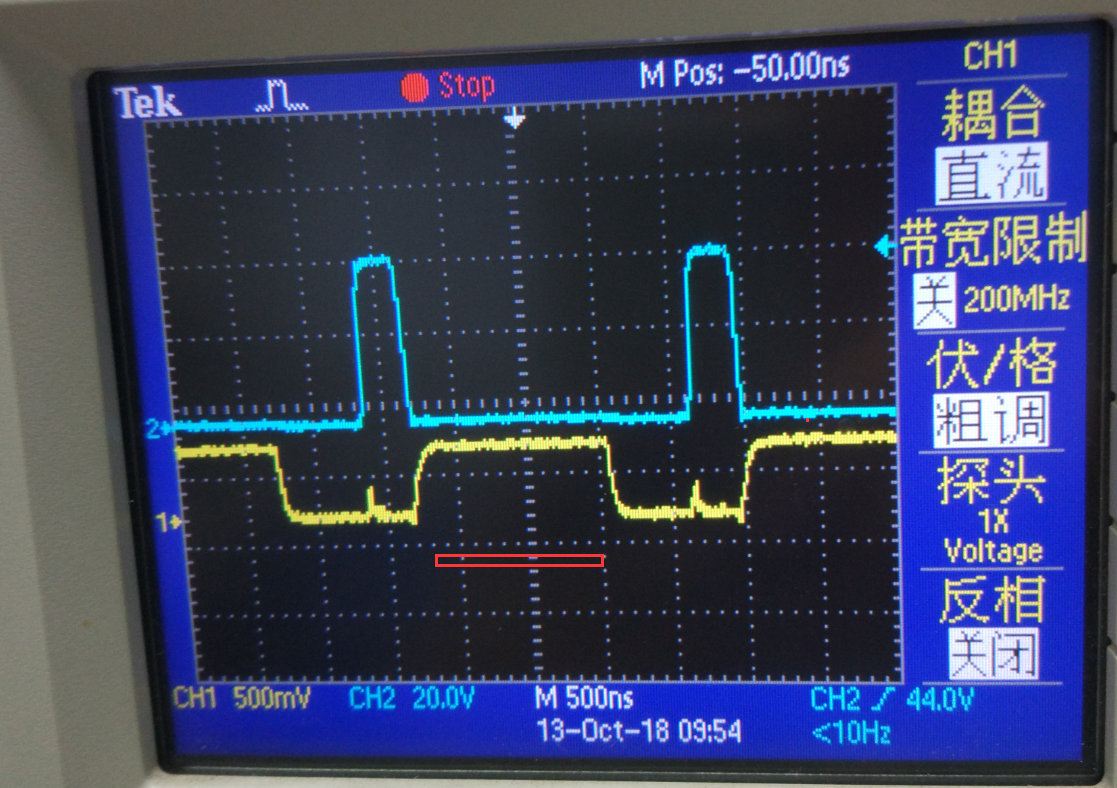

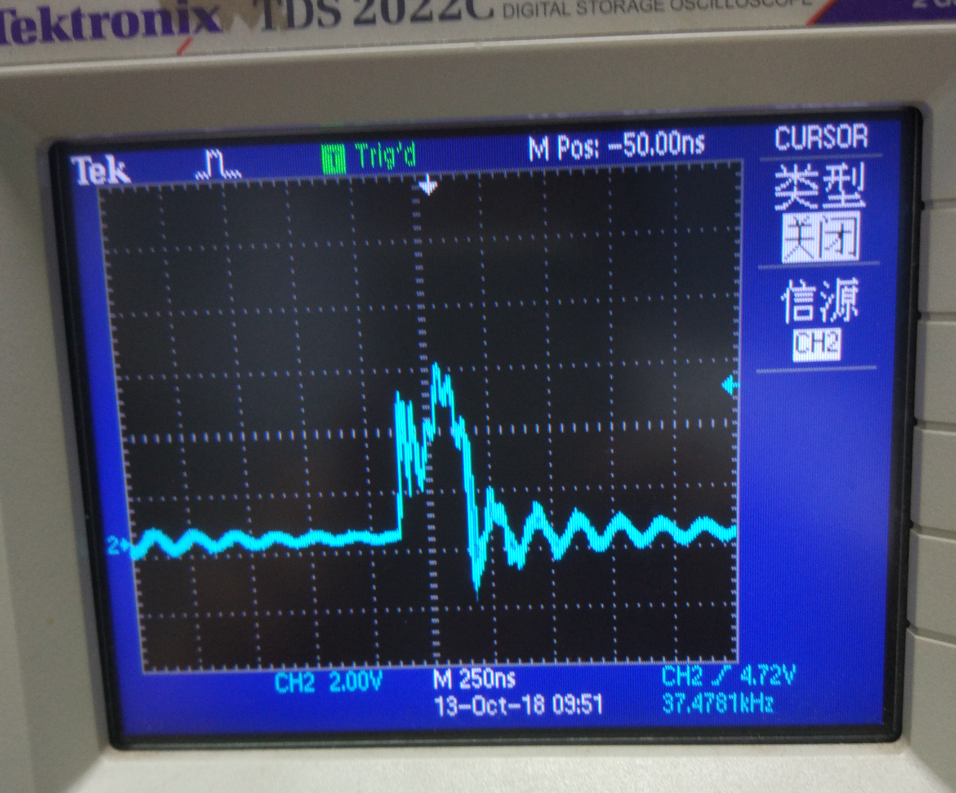

I have test the high MOS Vgs,the wave was very strange

It was seen like not as full work,I gusset if it is the reason why MOSFET was very hot,even the output is only 1A

So my main question is something case the IC and MOSFET hot,I hope someone can help me to solve this problem