Other Parts Discussed in Thread: TAS2505

Tool/software: Code Composer Studio

hello

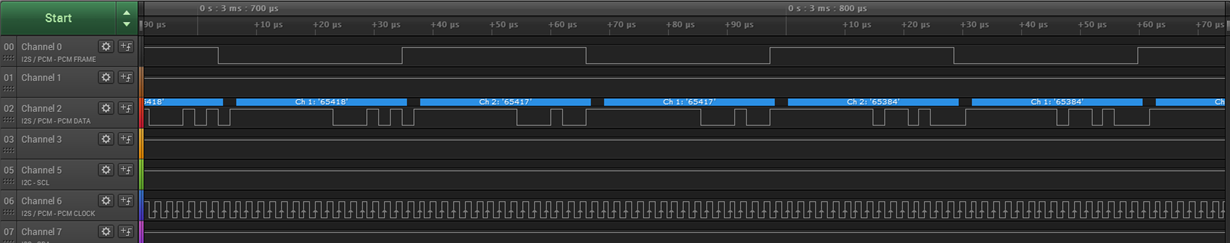

Now i use TAS2505 for design , i use 16k 16bit signal, the input clock is BCLK 512K ,

question 1: now , the MCLK is not connected , is the MCLK is ok not connected and only use BCLK for the TAS2505?

question 2: no mattery what clock I config , it always have noise , below is my config , could you help check is there is any issue ? thanks

u8 u8_Tas2025_InitConfigTable[]={

/// A2DP Sink - Enable Speaker Playback Class-D ///

///////////////// Initialization //////////////////

// Px, P0 Switch to Page 0

0x00, 0x00,

// Software Reset Register

// P0, R1, b0. Reset = SW Reset - Internal Registers

0x01, 0x01,

// Px, P1 Switch to Page 1

0x00, 0x01,

// LDO Control Register

// P1, R2, b5-4. AVDD LDO Output = 1.8V

// P1, R2, b3. PLL and HP Level Shifters = Power Up

0x02, 0x04,

////////////// Digital Configuration //////////////

// Px, P0 Switch to Page 0

0x00, 0x00,

0x04, 0x07,// BCLK , CODEC_CLKIN = PLL clock

0x05, 0x84,//PLL on , P = 1(D6-D4), R = 1(D3-D0)

0x06, 0x30,//PLL J = 24 (D5-D0)

0x07, 0x00,//PLL D(MSB)

0x08, 0x00,//PLL D(LSB)

0x0B, 0x81,//PLL NDAC = 3(D6-D0)

0x0C, 0x88,//PLL MDAC = 8(D6-D0)

0x0D, 0x01,//DAC DOSR = 128(MSB)(D1-D0)

0x0E, 0x00,//DAC DSOR = 128(LSB)(D7-D0)

0x1B, 0x00,//IIS , 16 bit ,BCLK WCLK

// Audio Interface Setting Register 2 - Data Offset

// P0, R28, b7-0. Data Offset = 1

0x1C, 0x01,

// DAC Instruction Set

// Filter A - Best Performance, PRB_P1

// P0, R60, b4-0. Processing Block: PRB_P1

0x3c, 0x01,

////////////// Analog Configuration //////////////

// Px, P1 Switch to Page 1

0x00, 0x01,

// REF, POR and LDO BGAP Control Register

// P1, R1, b4. Master Reference = Power Up

// P1, R1, b3. POR Power Control = Power Up

// P1, R1, b1. LDO Bandgap = Power Up

0x01, 0x10,

// Common Mode Control Register

// P1, R10, b6. Analog Output Common Mode = 0.9V

0x0A, 0x00,

// P1, R3, b5. DAC Mode = Enabled/Low-Power

// P1, R3, b4-2. DAC PTM Control = PTM_P3

0x03, 0x00,

// Speaker Volume Control 1 ?Best value = 0dB

// P1, R46, b6-0. Spk Analog Gain = 0dB

0x2E, 0x0F,

// Speaker Volume Control 2 ?Tune to best value

// P1, R48, b6-4. Spk Driver Gain = 12.0dB

0x30, 0x10,

// Speaker Amplifier Control 1

// P1, R45, b1. Spk Driver = Power Up/Reset

0x2D, 0x02,

//////////////////// Power On ///////////////////

// Px, P0 Switch to Page 0

0x00, 0x00,

// DAC Channel Setup Register 1

// P0, R63, b7. DAC Power = Power Up

// P0, R63, b5-4. DAC Path = Mix of L+R

// P0, R63, b1-0. Soft-Step Control = 1 step/WCLK

0x3F, 0xB4,

// DAC Channel Digital Volumer Control Register

// Max Value = 0dB, Min Value = -63dB. Not recommended to use + values

// P0, R65, b7-0. DAC Volume = 0dB (0)

0x41, 0x00,

// DAC Channel Setup Register 2

// P0, R64, b6-4. Auto Mute = Enabled / DC >100 consecutive inputs

// P0, R64, b3. Mute Control = Unmuted

0x40, 0x14

};