Hi There,

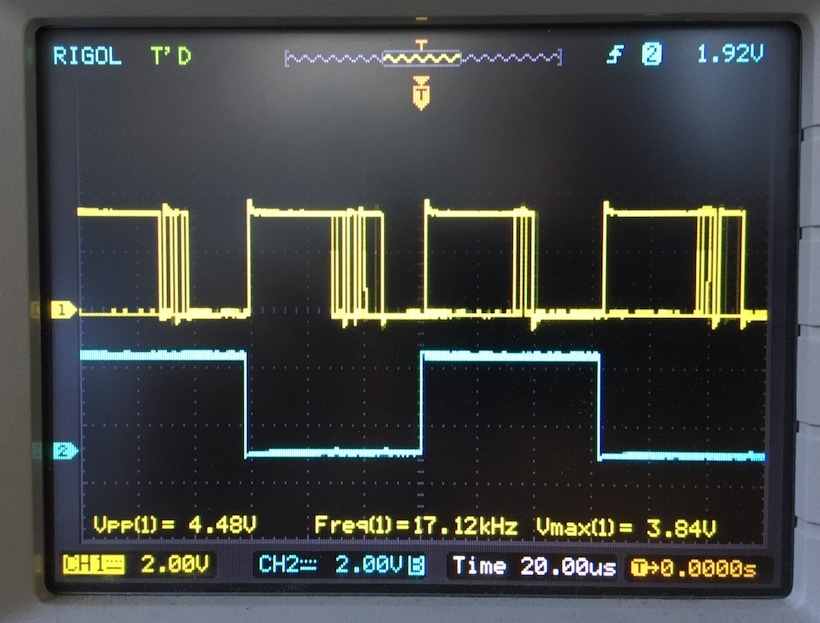

I'm feeding the PCM1808 ADC in master mode with an LRCLK, BCLK and a MCLK. Watching the DOUT signal one can see that it is mostly high on LRCLK transitions (regardless of the analog input). Any Idea why this is happening? I've checked the VREF pin, tested several devices, used another clock circuit at different sampling rates.

Thanks,

Gary