Other Parts Discussed in Thread: , TAS2505

Hi TI,

Due to MCU limitation, we do not have general audio sampling rate, such as 8k, 16k, 48kHz. Currently, we have 10k, 25k and 50kHz options. Below is the application circuit:

- TAS2505-Q1 is I2S slave without MCLK input

- Use BCLK as PLL clock input

- Only 5V as SPKVDD, 3V3 as IOVDD

- LDO_SEL is high, connect AVDD and DVDD together, using internal LDO

- I2S: BCLK=800kHz, WS=25kHz, 16bit depth

I have tested another media source with the same configuration but 48kHz sampling, it works. Then, I modified the clock setting to fit TAS2501-Q1 requirement. My setting is as below:

- BCLK is 800kHz and as PLL_CLKIN

- P=1, R=4, J=28, P=1

- PLL_CLK is 89.6MHz and as CODEC_CLKIN

- NDAC=2, DAC_CLK is 44.8MHz

- MDAC=7, DAC_MOD_CLK is 6.4MHz

- DOSR=256, DAC_fs is 25kHz

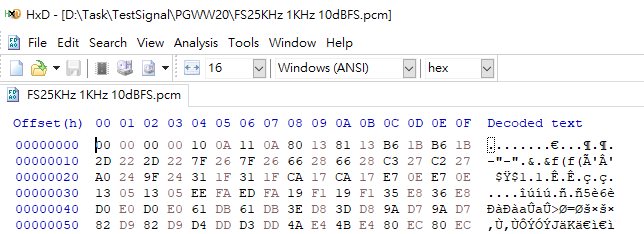

For more detail, please refer to attached config file.PGWW20_ClassD_playback_FS25k.cfg

However, I hear the high frequency tone, not 1kHz tone. What I would like to confirm are