Hi,

I am working on an audio project, I am using TLV320adc3100 for analog to digital conversion of the audio signal.

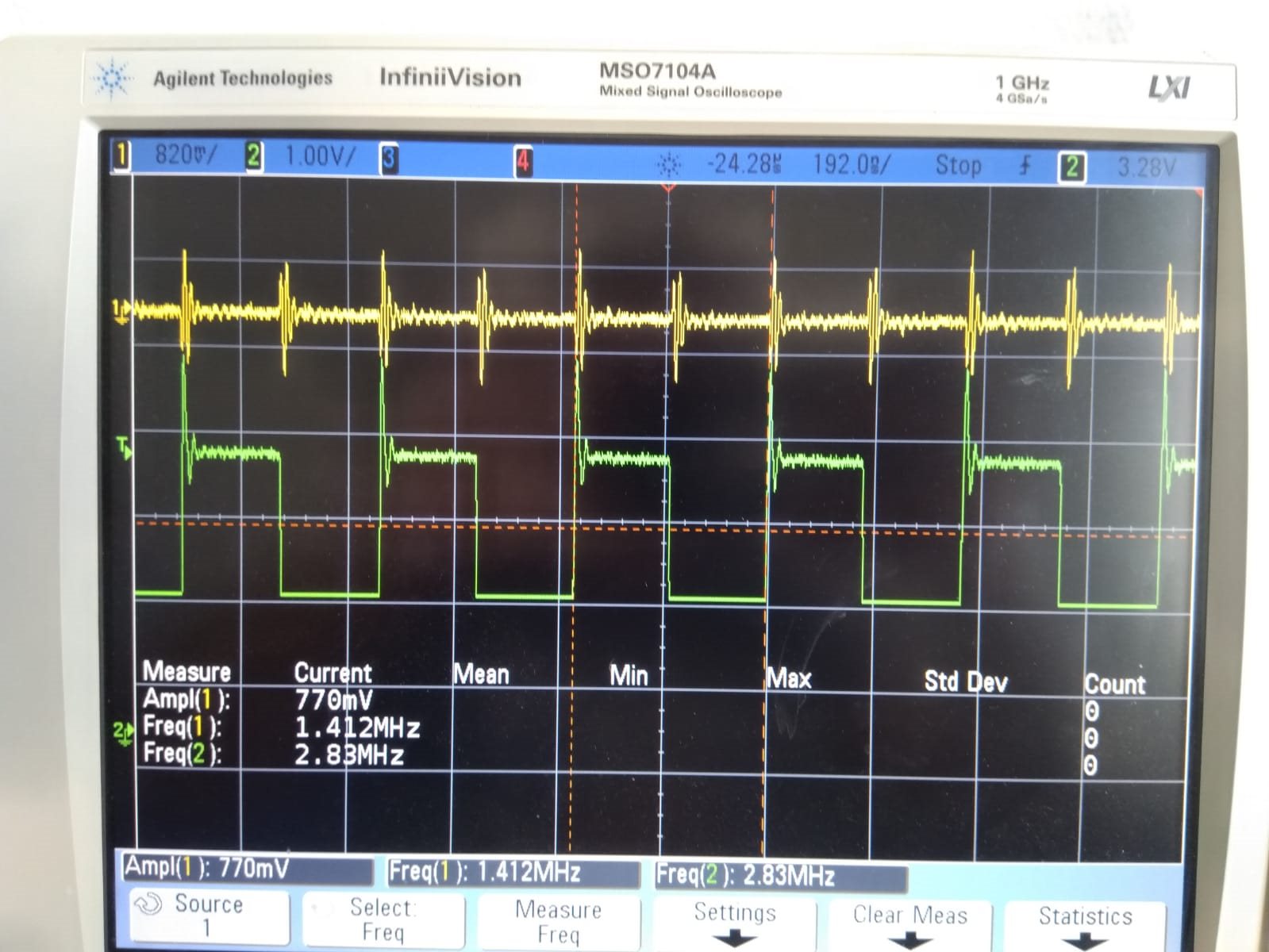

I am interfacing the adc with a raspberry pi (Host device) with i2c and configuring the registers as per my requirements in a python script using the read and write commands.

I want to use i2s format for serial communication.

Also, I am using the bclk(from i2s) as the pll clockin, and pll_clk as codec_clkin (configured via register 4).

I am not able to get any output.

Problems :

1. not able to write to register 1: (Software Reset), even if I write it as 1, again when I read the value it is 0.

2. is the clock configuration I mentioned above correct? or I need to provide a separate clock for the pll?

CAN ANYONE HELP PLEASE???