Dears:

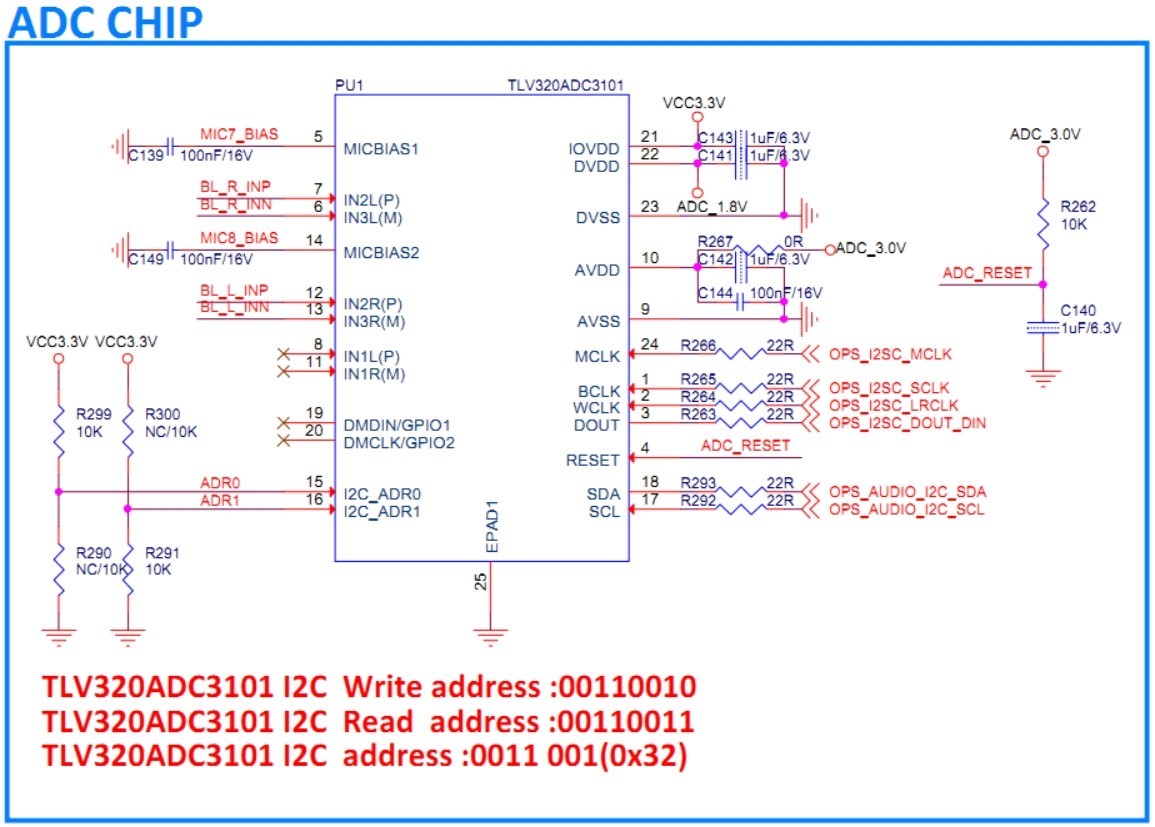

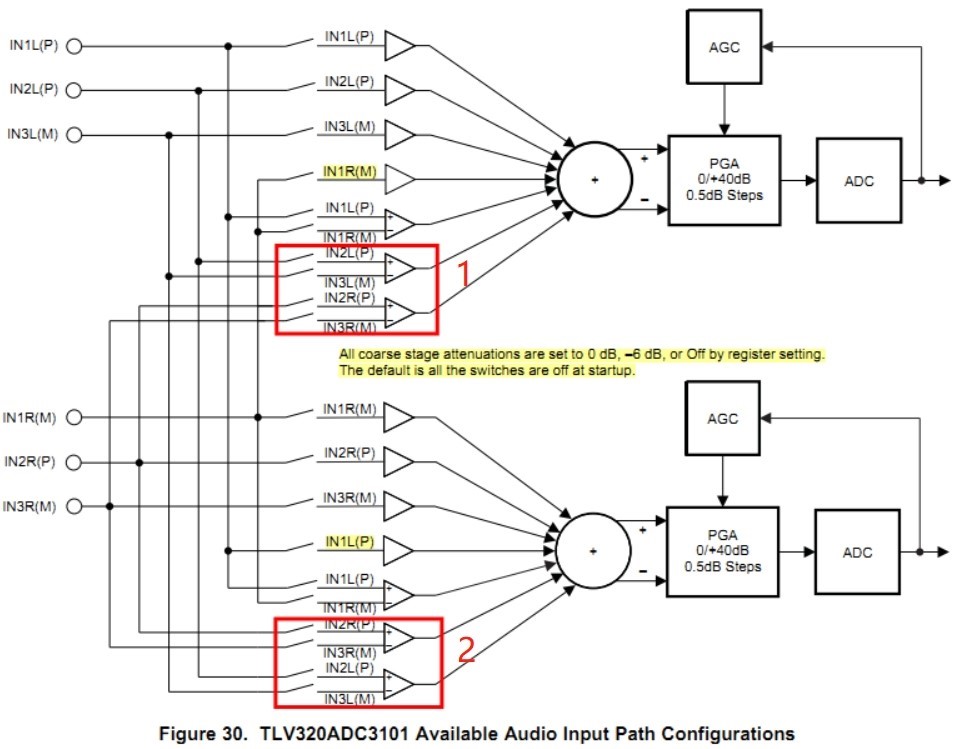

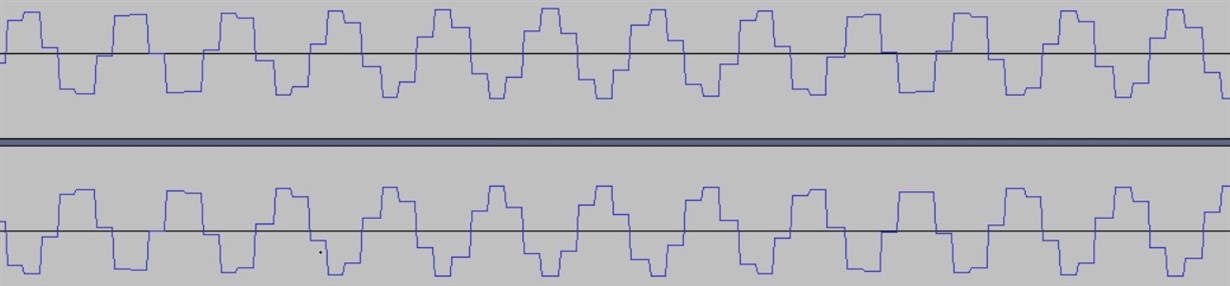

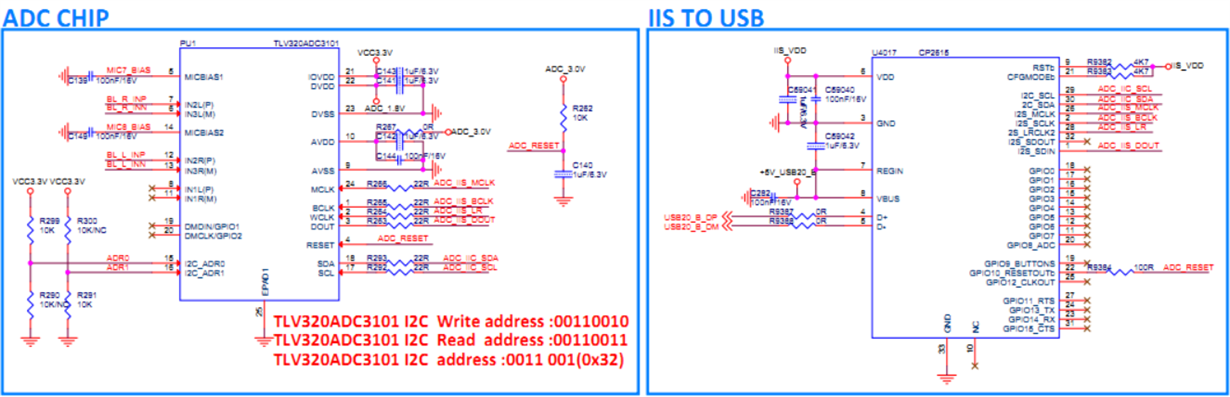

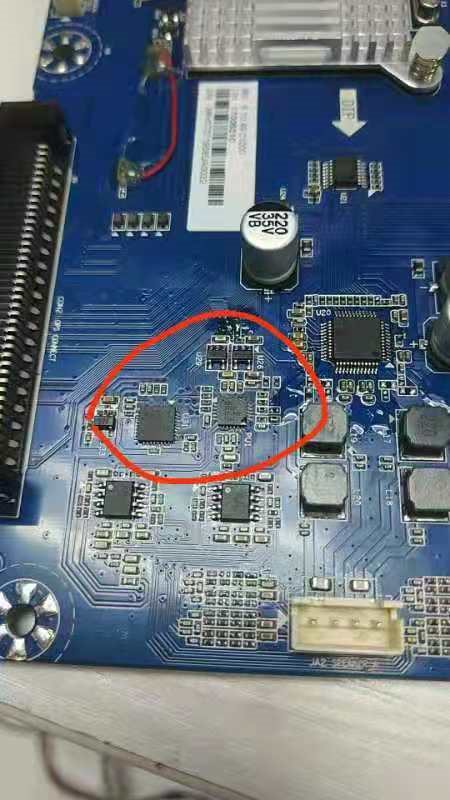

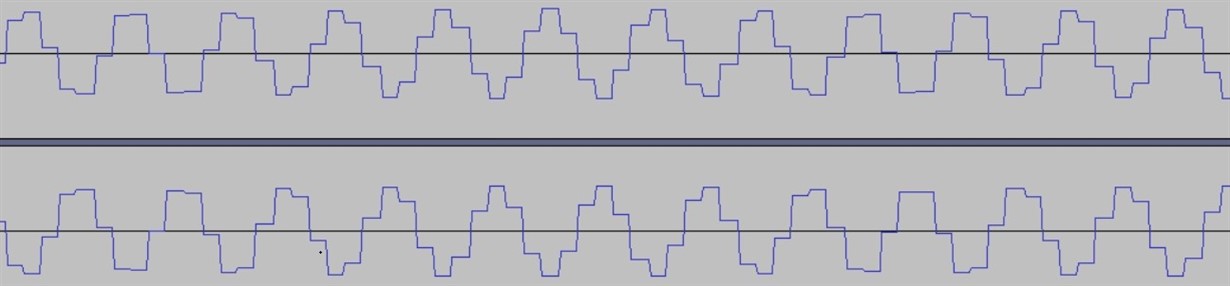

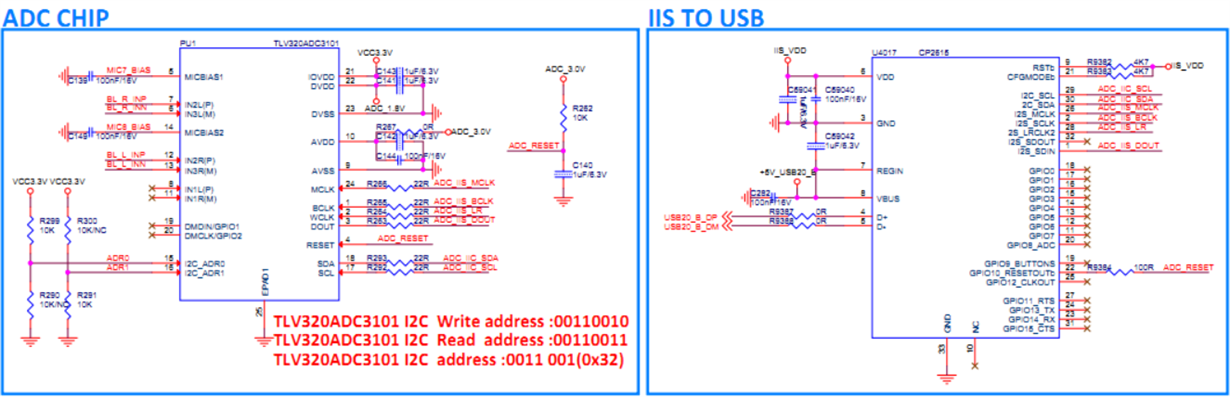

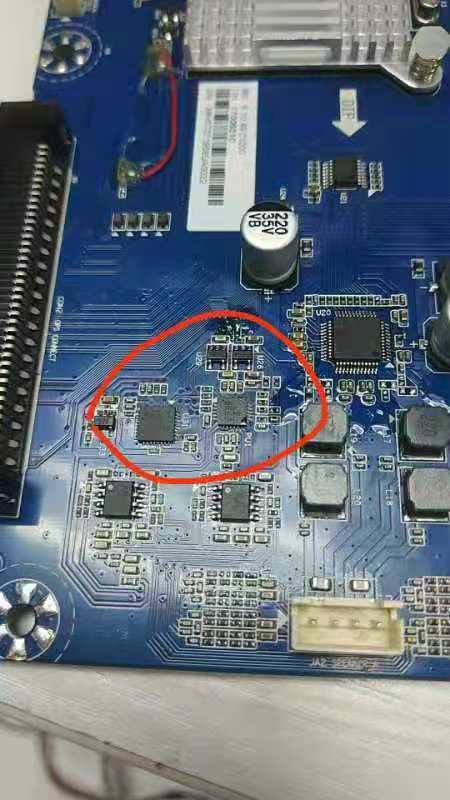

Could you kindly help to check schematic and the setting for getting sine wave.

delay_ms(100)

write(0x32, [0x00, 0x00])

write(0x32, [0x01, 0x01])

delay_ms(100)

write(0x32, [0x04, 0x00, 0x91, 0x08, 0x07, 0x80])

write(0x32, [0x12, 0x88, 0x82, 0x80])

write(0x32, [0x1B, 0x00])

write(0x32, [0x00, 0x01])

write(0x32, [0x33, 0x00])

write(0x32, [0x36, 0xB3])

write(0x32, [0x39, 0xB3])

write(0x32, [0x34, 0x3F])

write(0x32, [0x37, 0x3F])

write(0x32, [0x3B, 0x20, 0x20])

write(0x32, [0x00, 0x00])

write(0x32, [0x51, 0xC2, 0x00])