Hello.

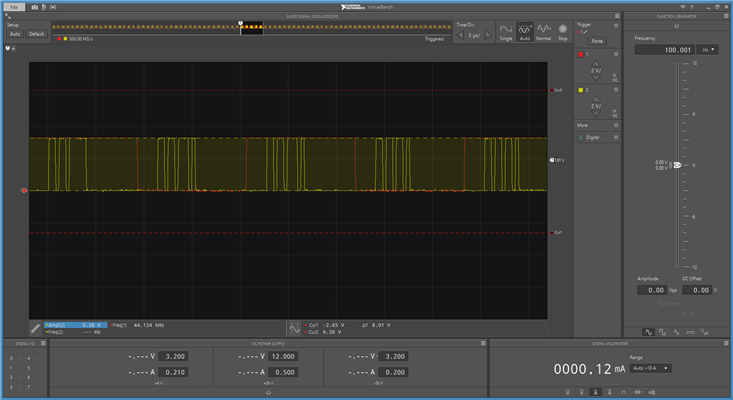

We have developed a code on PPS-GDE to perform filtering on analog microphone input and output it on the speaker left channel, headphones and I2S channels. Using a digital oscilloscope(image below) and recording on Audacity, we were able to verify I2S output and filtering according to our needs. The red is the WCLK and Yellow is DOUT.

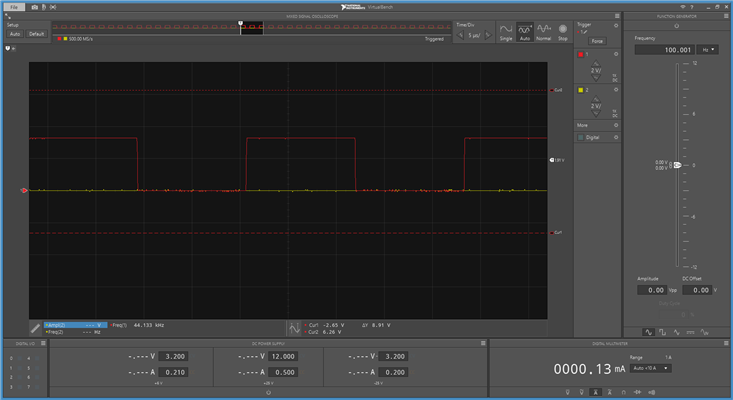

We then generated a header file on PPS and used I2C to the header instructions through the I2C channel. On doing so, we are getting an audio output on speaker and headphones but it seems like the output is not filtered and we are not getting any kind of output on the I2S channel DOUT as shown on the oscilloscope or Audacity as below. The red is the WCLK and Yellow is DOUT. As you can see, nothing is being transmitted on the DOUT line of I2S.

Below is my PFW on PPS-GDE. Also, I have attached the header file generated and Configuration file data. I suspect that the miniDSP A and D need to be turned on or enabled somehow when we use a master microcontroller or there is some standby mode that is handled by PPS by default but needs to be looked at by the user when using a microcontroller. I am using the paper titled 'Using the MSP430 Launchpad as a Standalone I2C Host' for designing the I2C code.

for Audio Products'

Config file

reg[0][1] = 0x01 ; S/W Reset

reg[0][4] = 0x03 ; PLL_CLKIN = MCLK = 11.2896 MHz., CODEC_CLKIN=PLL_CLK

reg[0][5] = 0x91 ; PLL Power Up, P = 1, R = 1

reg[0][6] = 0x08 ; J = 8

reg[0][7] = 0x00 ; D(13:8) = 0

reg[0][8] = 0x00 ; D(7:0) = 0 (CODEC_CLKIN = (PLL_CLKIN * R * J.D) / P = 90.3168 MHz.

reg[0][27] = 0x00 ; Mode = I2S, wordlength = 16

reg[0][53] = 0x12 ;

reg[43][95] = 0x00 ; (Bit 23-16) ------------ MSB ADC INST No. 383

reg[43][96] = 0x00 ; (Bit 15-8)

reg[43][97] = 0x00 ; (Bit 7-0)

reg[95][95] = 0x00 ; (Bit 23-16) ------------ MSB DAC INST No. 1023

reg[95][96] = 0x00 ; (Bit 15-8)

reg[95][97] = 0x00 ; (Bit 7-0)

IADC = %%prop(miniDSP_A_Cycles)

IDAC = %%prop(miniDSP_D_Cycles)

reg[0][60] = 0x40 ; DAC programmable mode, DAC miniDSP powered up even if DAC is powered down

reg[0][61] = 0x00 ; PRB_R5 05

PROGRAM_ADC

PROGRAM_DAC

%%if ("%%prop(FrameworkType)" == "AIC31XXApp2x1xAsynch" || "%%prop(FrameworkType)" == "AIC31XXApp2x1xSynch")

reg[0][13] = 0x00 ; DOSR = 32, DOSR(9:8) = 0

reg[0][14] = 0x20 ; DOSR = 32, DOSR(7:0) = 32 (DAC Fs = 5.6448 / 32 = 176.4 KHz.)

reg[0][16] = 0x02 ; Interpolation Ratio = 2

reg[0][20] = 0x20 ; AOSR = 32 (ADC Fs = 5.6448 / 32 = 176.4 KHz.)

reg[0][22] = 0x01 ; Decimation Ratio = 1

%%endif

%%if ("%%prop(FrameworkType)" == "AIC31XXApp4x2xAsynch" || "%%prop(FrameworkType)" == "AIC31XXApp4x2xSynch")

reg[0][13] = 0x00 ; DOSR = 64, DOSR(9:8) = 0

reg[0][14] = 0x40 ; DOSR = 64, DOSR(7:0) = 64 (DAC Fs = 5.6448 / 64 = 88.2 KHz.)

reg[0][16] = 0x04 ; Interpolation Ratio = 2

reg[0][20] = 0x40 ; AOSR = 64 (ADC Fs = 5.6448 / 64 = 88.2 KHz.)

reg[0][22] = 0x02 ; Decimation Ratio = 2

%%endif

%%if ("%%prop(FrameworkType)" == "AIC31XXApp8x4xAsynch" || "%%prop(FrameworkType)" == "AIC31XXApp8x4xSynch")

reg[0][13] = 0x00 ; DOSR = 128, DOSR(9:8) = 0

reg[0][14] = 0x80 ; DOSR = 128, DOSR(7:0) = 32 (DAC Fs = 5.6448 / 128 = 44.1 KHz.)

reg[0][16] = 0x08 ; Interpolation Ratio = 8

reg[0][20] = 0x80 ; AOSR = 128 (ADC Fs = 5.6448 / 128 = 44.1 KHz.)

reg[0][22] = 0x04 ; Decimation Ratio = 4

%%endif

reg[1][33] = 0x4e ; De-pop, Power on = 800 ms., Step time = 4 ms.

reg[1][31] = 0xc6 ; HPL and HPR powered up

reg[1][32] = 0xc6 ; SPL on

reg[1][35] = 0x50 ; LDAC routed to mixer, LMIC

reg[1][36] = 0x80 ; HPL on

reg[1][38] = 0xa8 ; -20 SPL vol 0dB

reg[1][40] = 0x16

reg[1][42] = 0x04 ; SPL unmute, gain 6dB

reg[1][46] = 0x0b ; MICBIAS

reg[0][83] = 0x1e ; ADC GAIN 15dB

reg[1][48] = 0x40 ; MIC is selected for left Mic PGA P @ 10k input impedance

reg[1][49] = 0x40 ; CM is selected for left Mic PGA M @ 10k input impedance

reg[0][63] = 0xd6 ; Powerup DAC left and right channels (soft step disable)

reg[0][64] = 0x00 ; Unmute DAC left and right channels

reg[0][81] = 0x80 ; Powerup ADC channel

reg[0][82] = 0x00 ; Unmute ADC channel

%%if ("%%prop(FrameworkType)" == "AIC31XXApp2x1xAsynch" || "%%prop(FrameworkType)" == "AIC31XXApp4x2xAsynch" || "%%prop(FrameworkType)" == "AIC31XXApp8x4xAsynch")

reg[0][11] = 0x82 ; DAC Powerup NDAC = 2 (DAC_MAC_CLK = 90.3168 MHz/2 = 45.1584 MHz.)

reg[0][12] = 0x88 ; DAC Powerup MDAC = 8 (DAC_MOD_CLK = 45.1584/8 = 5.6448 MHz.)

reg[0][18] = 0x84 ; ADC Powerup NADC = 4 (ADC_MAC_CLK = 90.3168 MHz/4 = 22.5792 MHz.)

reg[0][19] = 0x84 ; DAC Powerup MADC = 4 (ADC_MOD_CLK = 22.5792/4 = 5.6448 MHz.)

%%endif

%%if ("%%prop(FrameworkType)" == "AIC31XXApp2x1xSynch" || "%%prop(FrameworkType)" == "AIC31XXApp4x2xSynch" || "%%prop(FrameworkType)" == "AIC31XXApp8x4xSynch")

reg[0][11] = 0x84 ; DAC Powerup NDAC = 4 (DAC_MAC_CLK = 90.3168 MHz/4 = 22.5792 MHz.)

reg[0][12] = 0x84 ; DAC Powerup MDAC = 4 (DAC_MOD_CLK = 22.5792/4 = 5.6448 MHz.)

reg[0][18] = 0x84 ; ADC Powerup NADC = 4 (ADC_MAC_CLK = 90.3168 MHz/4 = 22.5792 MHz.)

reg[0][19] = 0x84 ; DAC Powerup MADC = 4 (ADC_MOD_CLK = 22.5792/4 = 5.6448 MHz.)

%%endif

%%if (%%prop(miniDSP_D_Adaptive) == 1)

reg[8][1] = 0x04 ; Adaptive mode enabled for DAC

%%endif

;-----------------------------------------------------------------------------------

; Clock and Interface Configuration

;-----------------------------------------------------------------------------------

; USB Audio supports 8kHz to 48kHz sample rates

; An external audio interface is required for 88.2kHz to 192kHz sample rates

;-----------------------------------------------------------------------------------

%%if (%%prop(SampleRate) == 176400 || %%prop(SampleRate) == 192000)

reg[ 0][ 5] = 0x91 ; P=1, R=1, J=8

reg[ 0][ 6] = 0x08 ; P=1, R=1, J=8

reg[ 0][ 7] = 0x00 ; D=0000 (MSB)

reg[ 0][ 8] = 0x00 ; D=0000 (LSB)

reg[ 0][ 4] = 0x03 ; PLL_clkin = MCLK, codec_clkin = PLL_CLK, PLL on

reg[ 0][ 12] = 0x88 ; MDAC = 8, divider powered on

reg[ 0][ 13] = 0x00 ; DOSR = 32 (MSB)

reg[ 0][ 14] = 0x20 ; DOSR = 32 (LSB)

reg[ 0][ 18] = 0x02 ; NADC = 2, divider powered off

reg[ 0][ 19] = 0x88 ; MADC = 8, divider powered on

reg[ 0][ 20] = 0x20 ; AOSR = 32

reg[ 0][ 11] = 0x82 ; NDAC = 2, divider powered on

%%endif

%%if (%%prop(SampleRate) == 88200 || %%prop(SampleRate) == 96000)

reg[ 0][ 5] = 0x91 ; P=1, R=1, J=8

reg[ 0][ 6] = 0x08 ; P=1, R=1, J=8

reg[ 0][ 7] = 0x00 ; D=0000 (MSB)

reg[ 0][ 8] = 0x00 ; D=0000 (LSB)

reg[ 0][ 4] = 0x03 ; PLL_clkin = MCLK, codec_clkin = PLL_CLK, PLL on

reg[ 0][ 12] = 0x88 ; MDAC = 8, divider powered on

reg[ 0][ 13] = 0x00 ; DOSR = 64 (MSB)

reg[ 0][ 14] = 0x40 ; DOSR = 64 (LSB)

reg[ 0][ 18] = 0x02 ; NADC = 2, divider powered off

reg[ 0][ 19] = 0x88 ; MADC = 8, divider powered on

reg[ 0][ 20] = 0x40 ; AOSR = 64

reg[ 0][ 11] = 0x82 ; NDAC = 2, divider powered on

%%endif

%%if (%%prop(SampleRate) == 44100 || %%prop(SampleRate) == 48000)

reg[ 0][ 5] = 0x91 ; P=1, R=1, J=8

reg[ 0][ 6] = 0x08 ; P=1, R=1, J=8

reg[ 0][ 7] = 0x00 ; D=0000 (MSB)

reg[ 0][ 8] = 0x00 ; D=0000 (LSB)

reg[ 0][ 4] = 0x03 ; PLL_clkin = MCLK, codec_clkin = PLL_CLK, PLL on

reg[ 0][ 12] = 0x88 ; MDAC = 8, divider powered on

reg[ 0][ 13] = 0x00 ; DOSR = 128 (MSB)

reg[ 0][ 14] = 0x80 ; DOSR = 128 (LSB)

reg[ 0][ 18] = 0x02 ; NADC = 2, divider powered off

reg[ 0][ 19] = 0x88 ; MADC = 8, divider powered on

reg[ 0][ 20] = 0x80 ; AOSR = 128

reg[ 0][ 11] = 0x82 ; NDAC = 2, divider powered on

%%endif

%%if (%%prop(SampleRate) == 32000)

reg[ 0][ 5] = 0x91 ; P=1, R=1, J=8

reg[ 0][ 6] = 0x08 ; P=1, R=1, J=8

reg[ 0][ 7] = 0x00 ; D=0000 (MSB)

reg[ 0][ 8] = 0x00 ; D=0000 (LSB)

reg[ 0][ 4] = 0x03 ; PLL_clkin = MCLK, codec_clkin = PLL_CLK, PLL on

reg[ 0][ 12] = 0x88 ; MDAC = 8, divider powered on

reg[ 0][ 13] = 0x00 ; DOSR = 192 (MSB)

reg[ 0][ 14] = 0xc0 ; DOSR = 192 (LSB)

reg[ 0][ 18] = 0x02 ; NADC = 2, divider powered off

reg[ 0][ 19] = 0x8c ; MADC = 12, divider powered on

reg[ 0][ 20] = 0x80 ; AOSR = 128

reg[ 0][ 11] = 0x82 ; NDAC = 2, divider powered on

%%endif

%%if (%%prop(SampleRate) == 22050 || %%prop(SampleRate) == 24000)

reg[ 0][ 5] = 0x91 ; P=1, R=1, J=8

reg[ 0][ 6] = 0x08 ; P=1, R=1, J=8

reg[ 0][ 7] = 0x00 ; D=0000 (MSB)

reg[ 0][ 8] = 0x00 ; D=0000 (LSB)

reg[ 0][ 4] = 0x03 ; PLL_clkin = MCLK, codec_clkin = PLL_CLK, PLL on

reg[ 0][ 12] = 0x88 ; MDAC = 8, divider powered on

reg[ 0][ 13] = 0x01 ; DOSR = 256 (MSB)

reg[ 0][ 14] = 0x00 ; DOSR = 256 (LSB)

reg[ 0][ 18] = 0x02 ; NADC = 2, divider powered off

reg[ 0][ 19] = 0x90 ; MADC = 16, divider powered on

reg[ 0][ 20] = 0x80 ; AOSR = 128

reg[ 0][ 11] = 0x82 ; NDAC = 2, divider powered on

%%endif

%%if (%%prop(SampleRate) == 16000)

reg[ 0][ 5] = 0x91 ; P=1, R=1, J=24

reg[ 0][ 6] = 0x18 ; P=1, R=1, J=24

reg[ 0][ 7] = 0x00 ; D=0000 (MSB)

reg[ 0][ 8] = 0x00 ; D=0000 (LSB)

reg[ 0][ 4] = 0x03 ; PLL_clkin = MCLK, codec_clkin = PLL_CLK, PLL on

reg[ 0][ 12] = 0x88 ; MDAC = 8, divider powered on

reg[ 0][ 13] = 0x01 ; DOSR = 384 (MSB)

reg[ 0][ 14] = 0x80 ; DOSR = 384 (LSB)

reg[ 0][ 18] = 0x02 ; NADC = 2, divider powered off

reg[ 0][ 19] = 0x98 ; MADC = 24, divider powered on

reg[ 0][ 20] = 0x80 ; AOSR = 128

reg[ 0][ 11] = 0x82 ; NDAC = 2, divider powered on

%%endif

%%if (%%prop(SampleRate) == 11025)

reg[ 0][ 5] = 0x91 ; P=1, R=1, J=16

reg[ 0][ 6] = 0x10 ; P=1, R=1, J=16

reg[ 0][ 7] = 0x00 ; D=0000 (MSB)

reg[ 0][ 8] = 0x00 ; D=0000 (LSB)

reg[ 0][ 4] = 0x03 ; PLL_clkin = MCLK, codec_clkin = PLL_CLK, PLL on

reg[ 0][ 12] = 0x88 ; MDAC = 8, divider powered on

reg[ 0][ 13] = 0x02 ; DOSR = 512 (MSB)

reg[ 0][ 14] = 0x00 ; DOSR = 512 (LSB)

reg[ 0][ 18] = 0x02 ; NADC = 2, divider powered off

reg[ 0][ 19] = 0xa0 ; MADC = 32, divider powered on

reg[ 0][ 20] = 0x80 ; AOSR = 128

reg[ 0][ 11] = 0x82 ; NDAC = 2, divider powered on

%%endif

%%if (%%prop(SampleRate) == 8000)

reg[ 0][ 5] = 0x91 ; P=1, R=1, J=24

reg[ 0][ 6] = 0x18 ; P=1, R=1, J=24

reg[ 0][ 7] = 0x00 ; D=0000 (MSB)

reg[ 0][ 8] = 0x00 ; D=0000 (LSB)

reg[ 0][ 4] = 0x03 ; PLL_clkin = MCLK, codec_clkin = PLL_CLK, PLL on

reg[ 0][ 12] = 0x88 ; MDAC = 8, divider powered on

reg[ 0][ 13] = 0x03 ; DOSR = 768 (MSB)

reg[ 0][ 14] = 0x00 ; DOSR = 768 (LSB)

reg[ 0][ 18] = 0x02 ; NADC = 2, divider powered off

reg[ 0][ 19] = 0xb0 ; MADC = 48, divider powered on

reg[ 0][ 20] = 0x80 ; AOSR = 128

reg[ 0][ 11] = 0x82 ; NDAC = 2, divider powered on

%%endifHeader file generated by PPS

6136.base_main_Rate44_pps_driver.h

Any insight or help will be greatly appreciated!

Thanks,

Souvik.