Hello,

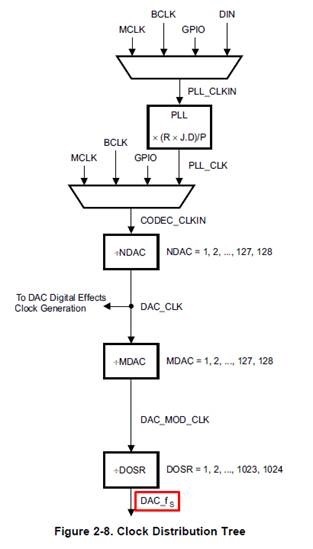

I have question regarding ADC_fs in TAS2505. Clock distribution tree from "Reference guide" is shown below:

There are many settings having influence over DAC_fs: R, J, D, P in the PLL and additionally NDAC, MDAC, DOSR.

My question is if the DAC_fs must be equal or be integer multiplication (or division) of the sample rate (WCLK) on the I2S input?

I use TAS2505EVM evalboard and noticed there is not possible to change I2S WCLK on that board. It is fixed on 48kHz regardless of sample rate of the audio file being played from PC. Probably the streaming controller (TAS1020) on that board takes care to provide such frequency and it is not possible to change it.

When playing with digital settings in the TAS2505EVM GUI I can set different DAC_fs values (having constant WCLK 48kHz) and these changes in DAC_fs have big influence over sound quality. In the device where I use TAS2505 I can set different sample frequency (WCLK). I do not use MCLK as DAC clock source, but BCLK with the PLL. So I guess I need to choose correct I2S sample rate and DAC_fs to get optimal sound quality, but I don't know answer to the question I have asked above.

Thank you and best regards / Maciej