Other Parts Discussed in Thread: CSD95373AQ5M, CSD

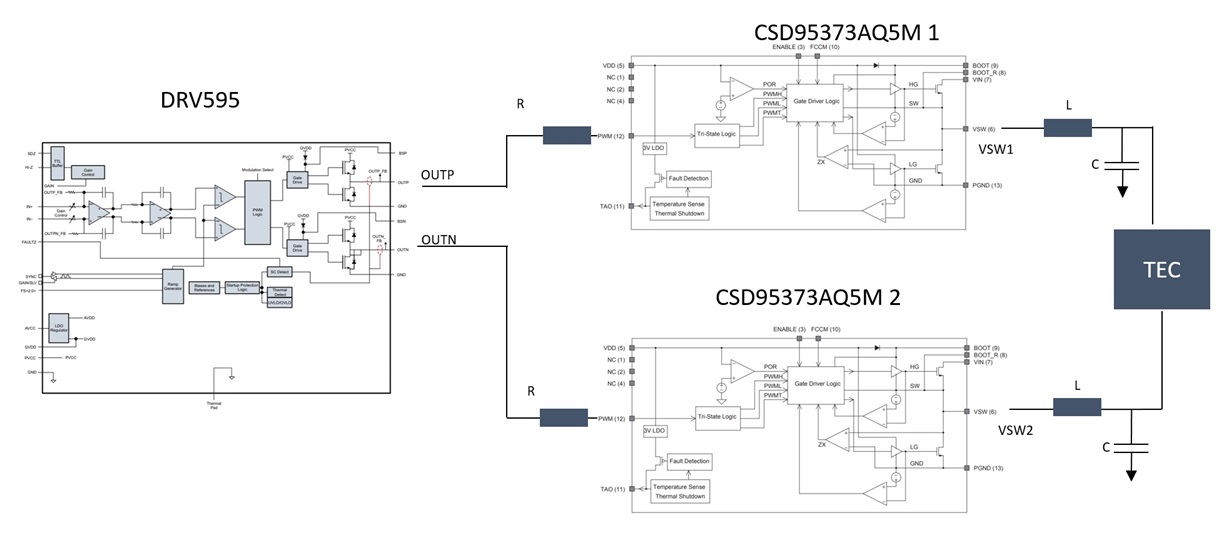

I have been using the DRV595 to drive a TEC with success (4A, 12VDC) however I now need more current (up to 10A). Is there a higher current version of this IC or alternatively is there a similar driver which I can interface with external mosfets? Perhaps a monolithic high power H-Bridge IC? Like the DRV595 it would be ideal to drive the differential input single ended and run the driver at a minium of 400kHz in order to keep component size and electrical noise/ripple to a minimum for the TEC.

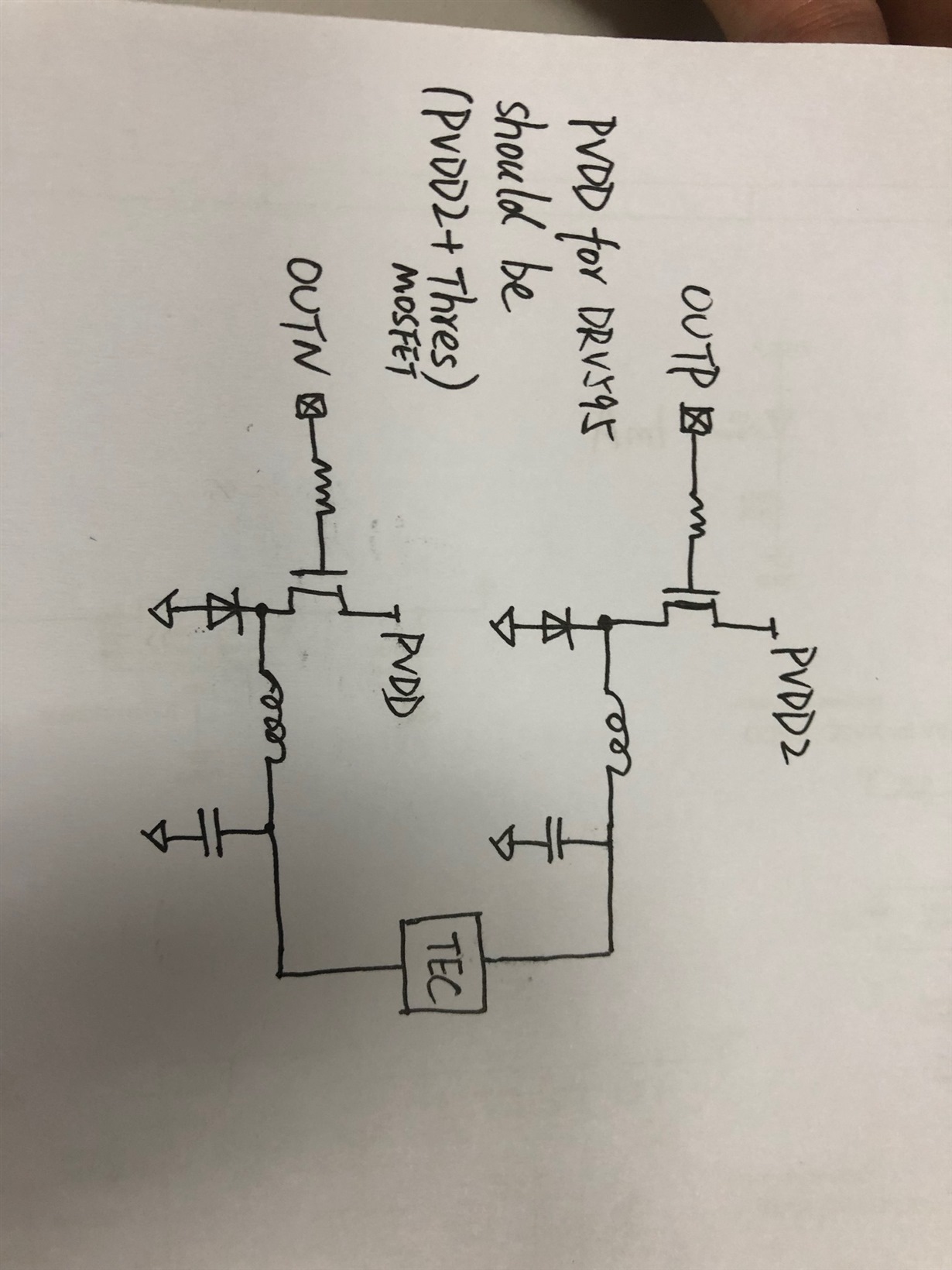

Is there a reason I cannot use a Synchronous Buck NexFET™ Power Stage (CSD95373AQ5M or similar) to allow higher currents? If the PWM outputs from the DRV595 are run via an appropriate resistive network to the PWM inputs on the CSD95373AQ5M then much higher currents can then be obtained?

Thanks!