Tool/software: WEBENCH® Design Tools

Dear Technical Support Team,

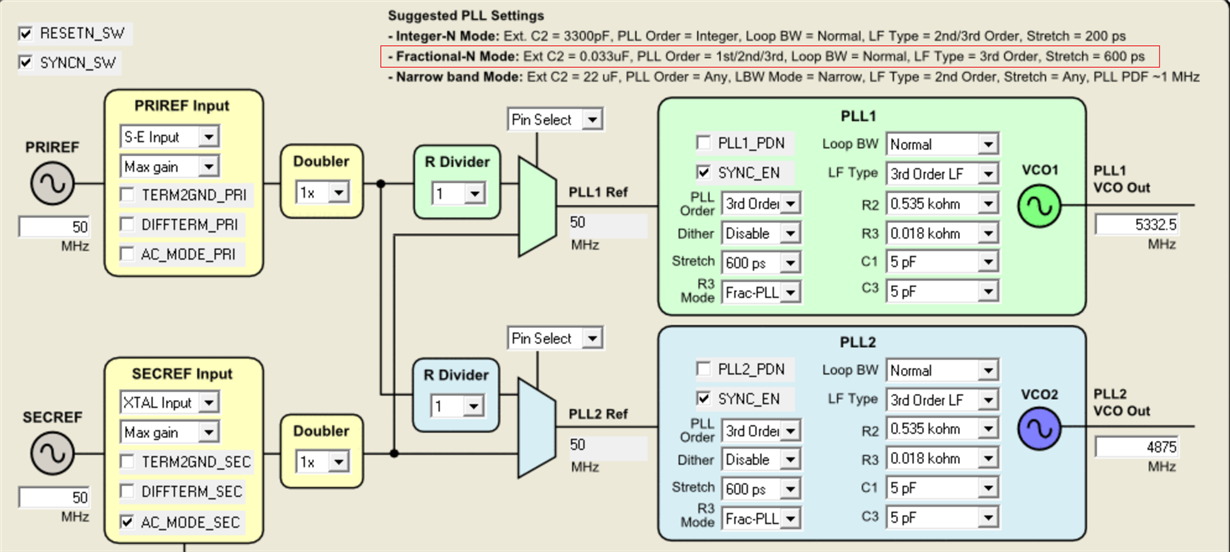

I'd like to implement appropriate PLL settings. Especially loop filter with WEBENCH.

Here is my WEBENCH project.

https://webench.ti.com/wb5/OpenPublicSharedProject.jsp?id=153EC8632C794927&s=c

I changed from auto value to C2=33nF myself on Webench (Basic ⇒Advanced mode on loop filter tab)

In may case, PLL settings are based on fractional value. So I should select 33nF based on Code Loader suggestion below.

■Questions,

I'd like to set minimum jitter implementation.

Could you check my webench and code loader?

If I have mistake, could you point out?

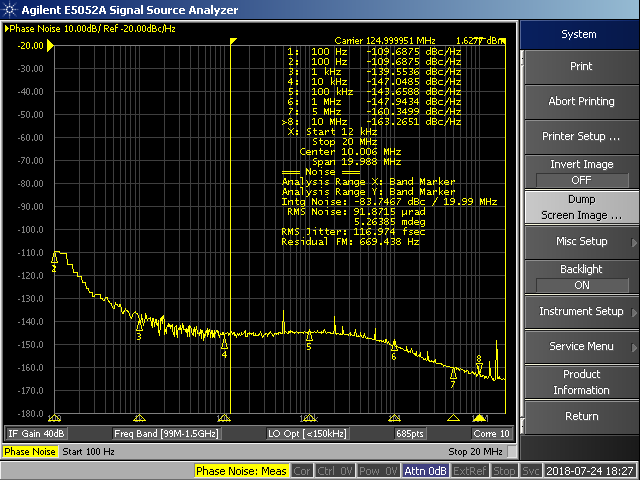

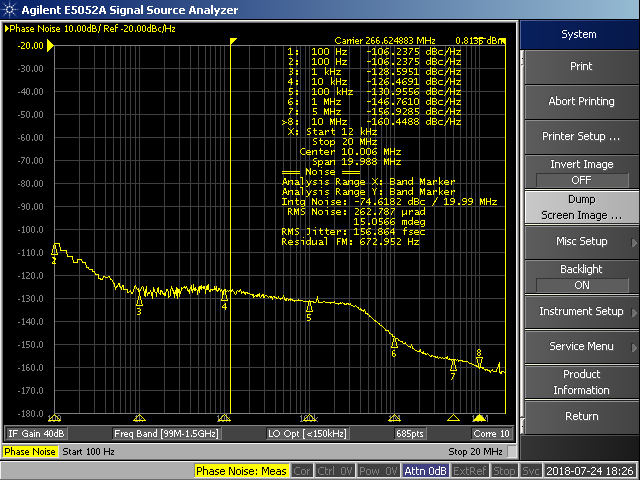

■My target clock

Input Frequency:50MHz

Output Frequencies: 266.625MHz LVDS & 125MHz LVDS

Output clock Jitter: inside 10ps peak to peak

■My project (Webench and Code Loader)

Webench

https://webench.ti.com/wb5/OpenPublicSharedProject.jsp?id=153EC8632C794927&s=c

Code Loader

(Could you change from .pdf to .mac? E2E doesn't accept .mac for upload)

Best Regards,

ttd