Hi,

I am currently trying to configure the CDCI6214 to be implemented in future projects. Even though I did read the given data sheet (rev.B) and forum posts I cant solve my problem.

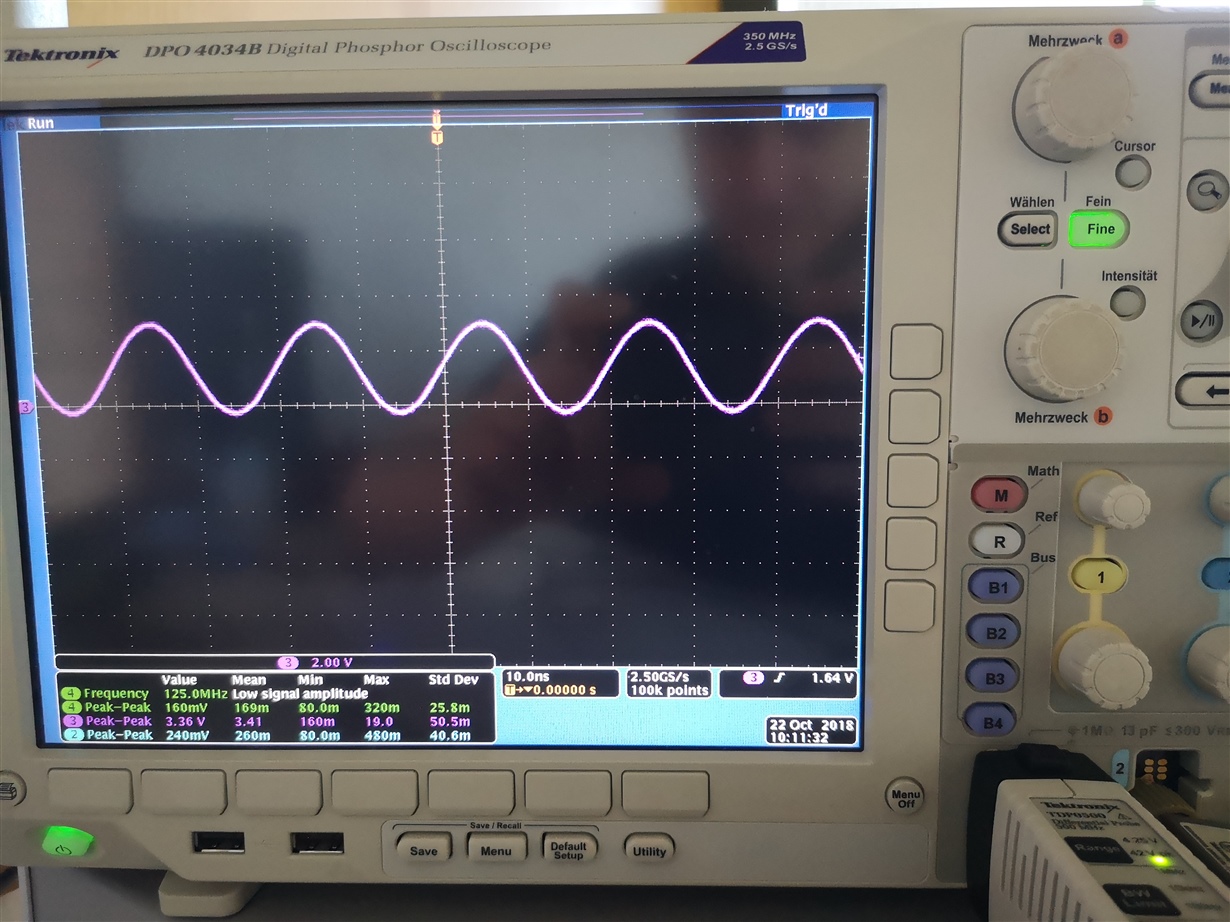

I successfully programmed the device via I2C to produce a bypass-signal through output Y0. But I cant get a output signal on any other output channel. I already tried various different combination.

A STM32 Nucleo L452RE is used for the I2C connection. I am leaving the EEPROMSEL and REFSEL pin floating while selecting the REF-Input via ref_mux. As a input signal I am using a 25Mhz square-wave which is generated with a Arbitrary Generator.

I am using the GPIO1-Pin to check the PLL-lock. Even though I used the values from Table2. (first row) and settings from Figure33. I cant get the PLL to lock.

I transmitted the programming the registers in this order:

Register Data Description

_________|________|__________________

0x00,0x0F,0x10,0x37 set ee_lock

0x00,0x28,0x00,0x08 set channel 1 on 1.8V

0x00,0x2E,0x00,0x08 set Channel 2 on 1.8V

0x00,0x34,0x00,0x08 set channel 3 on 1.8V

0x00,0x3A,0x00,0x08 set channel 4 on 1.8V

0x00,0x42,0x02,0x00

0x00,0x3F,0x02,0x10

0x00,0x3E,0x42,0x10

0x00,0x3D,0x15,0x00

0x00,0x3C,0x00,0x18

0x00,0x3B,0x00,0x63

0x00,0x3A,0x00,0x08

0x00,0x39,0x00,0x71

0x00,0x38,0x00,0x04

0x00,0x37,0x00,0x00

0x00,0x36,0x00,0x00

0x00,0x35,0x80,0x00

0x00,0x34,0x00,0x08

0x00,0x33,0x06,0x71

0x00,0x32,0x00,0x04

0x00,0x31,0x00,0x00

0x00,0x30,0x00,0x00

0x00,0x2F,0x80,0x00

0x00,0x2E,0x00,0x08

0x00,0x2D,0x00,0x71

0x00,0x2C,0x00,0x09

0x00,0x2B,0x00,0x00

0x00,0x2A,0x00,0x00

0x00,0x29,0x80,0x00

0x00,0x28,0x00,0x08

0x00,0x27,0x06,0x79

0x00,0x26,0x30,0x09

0x00,0x25,0x00,0x03

0x00,0x24,0x00,0x00

0x00,0x23,0x80,0x00

0x00,0x21,0x00,0x07

0x00,0x1F,0x1E,0x72

0x00,0x1E,0x51,0x40

0x00,0x1D,0x00,0x0C

0x00,0x1C,0x00,0x00

0x00,0x1B,0x0E,0x00

0x00,0x1A,0x0B,0x14

0x00,0x18,0x06,0x01

0x00,0x11,0x06,0xC4

0x00,0x10,0x92,0x1F

0x00,0x0F,0x10,0x37

0x00,0x0E,0x00,0x00

0x00,0x0D,0x00,0x00

0x00,0x0C,0x00,0x00

0x00,0x0B,0x00,0x00

0x00,0x0A,0x00,0x00

0x00,0x09,0x00,0x00

0x00,0x08,0x00,0x00

0x00,0x07,0x00,0x00

0x00,0x06,0x00,0x00

0x00,0x05,0x00,0x00

0x00,0x04,0x00,0x54

0x00,0x03,0x00,0x00

0x00,0x02,0x00,0x30

0x00,0x01,0x6B,0x32

0x00,0x00,0x10,0x40

Also I could not find out which value the "mode"-bit from table19. should have and what it's for.

Further there is a "Recommended Programming Procedure" described in section 8.5.1. It says that you should program the register in descending order from 0x44 to 0x00.

Is this only meant for programming EEPROM because there is no 0x44 register in register maps section 8.6.

Many Thanks

Maximilian Rentschler