Dean,

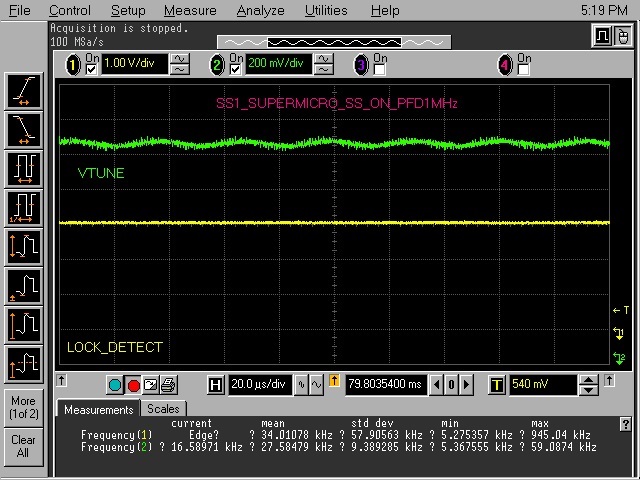

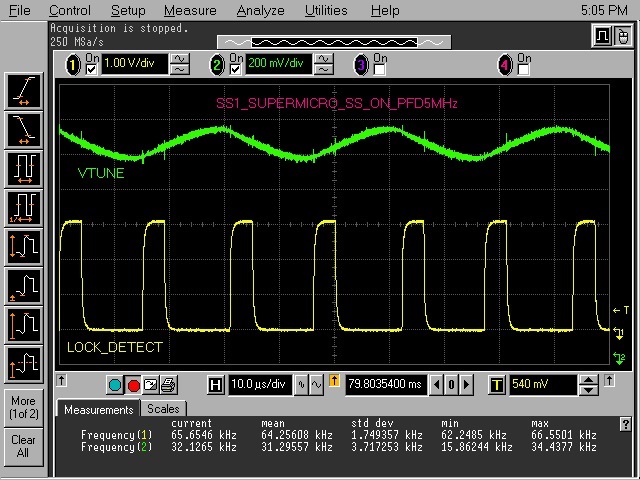

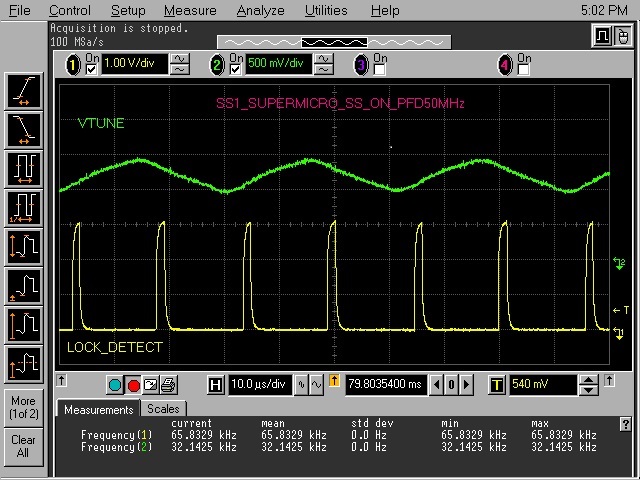

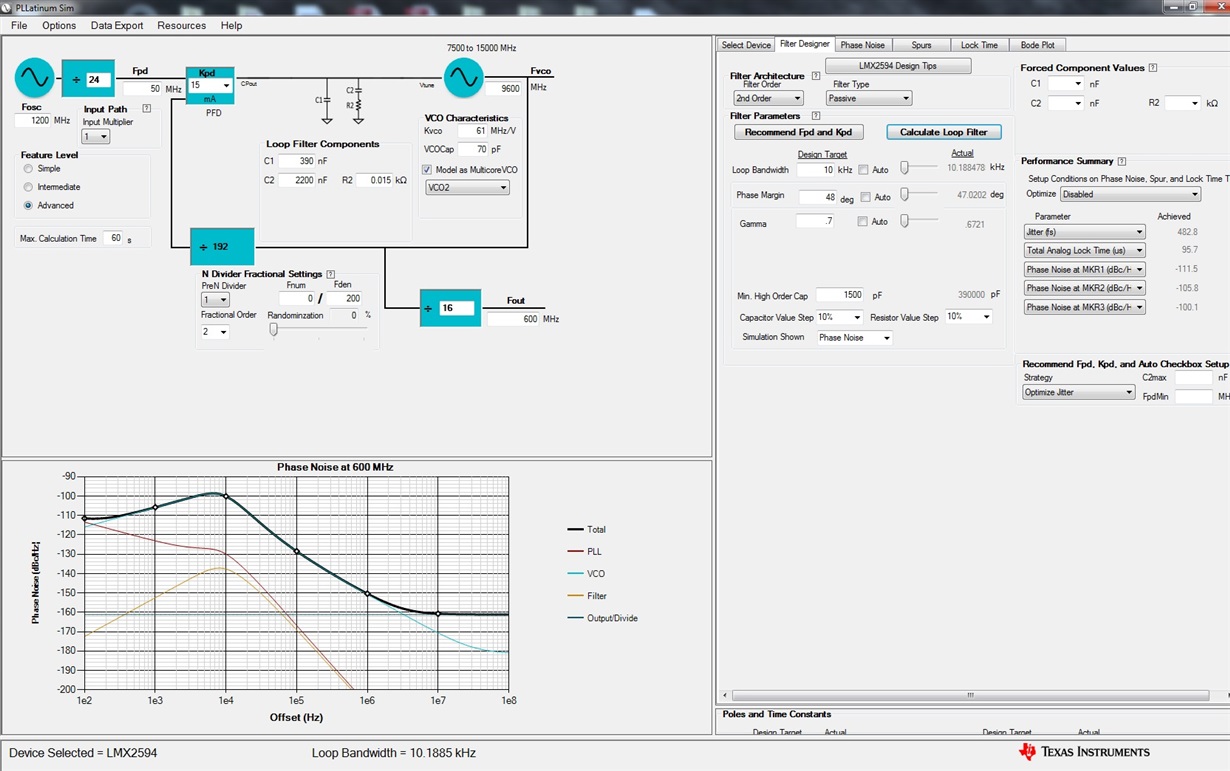

As I have previously posted in this forum, we have been attempting to use the LMX2594 to generate a deterministic, edge-locked 600MHz output clock derived from a 1.2GHz differential clock source. This source is the standard JEDEC clock provided on a DDR4 (DIMM) socket. This clock is driven with spread spectrum modulation. JEDEC specifies a spread-spectrum frequency deviation of 5000 PPM from the fundamental at a modulation period of 30KHz.

So far, we have not been able to achieve deterministic phase-lock with the LMX2594 in a spread spectrum scenario. (However, we can achieve phase-frequency lock when spread spectrum is disabled). Since there are other JEDEC-specified devices and FPGAs that employ PLLs that are spread-spectrum tolerant, we were expecting that a device as sophisticated as the LMX2594 would have a similar capability. If not, can TI confirm that the LMX2594 is inherently not compatible with or tolerant of an OSC input clock using spread spectrum modulation as described above? Or conversely, can TI provide us with further guidance as to how the LMX2594 and/or support circuitry be adjusted to meet this design goal?

Thanks,

- Ken