Other Parts Discussed in Thread: , CODELOADER

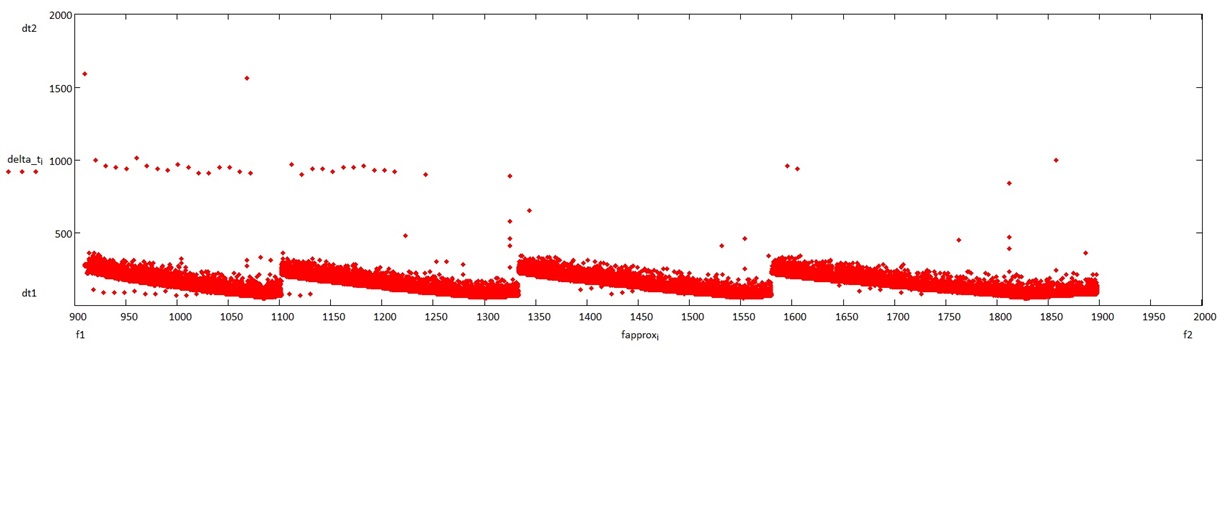

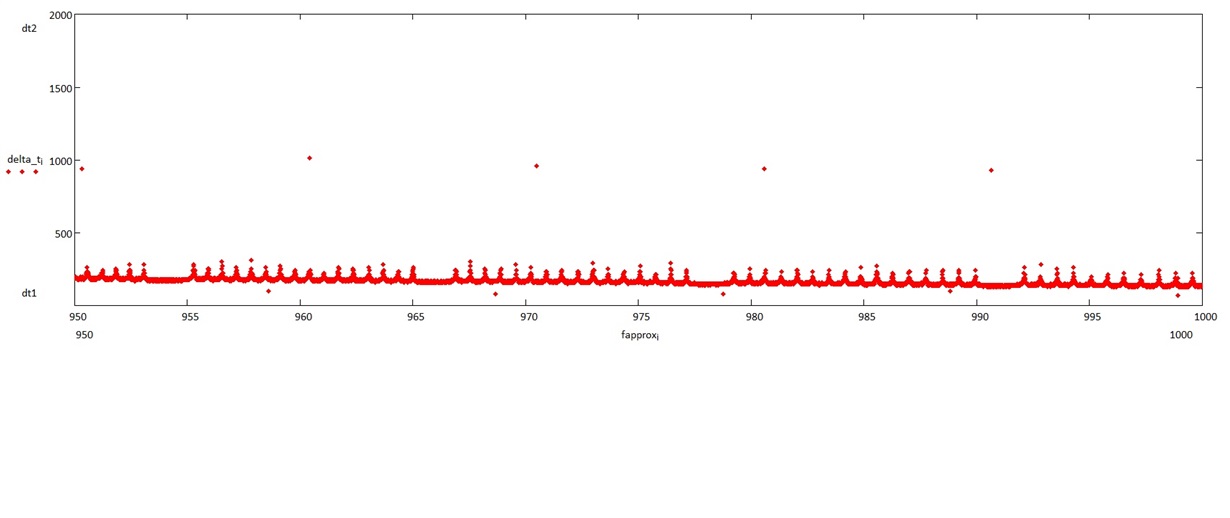

We are using the LMX2581 over a wide range with a comparably small step size, f=0.9-1.8 and 1.8-3.6 GHz, step df= 1-2kHz.

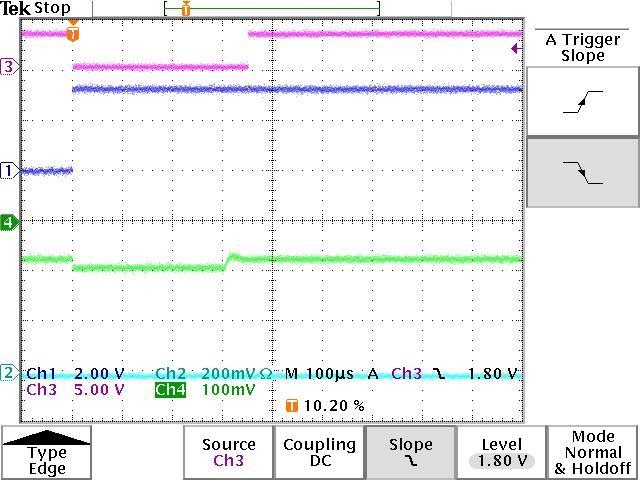

We have noticed distinct frequency regions where the VCO calibration time takes unusually long, in some regions few ms in

one very pronounced region up to 10 ms!

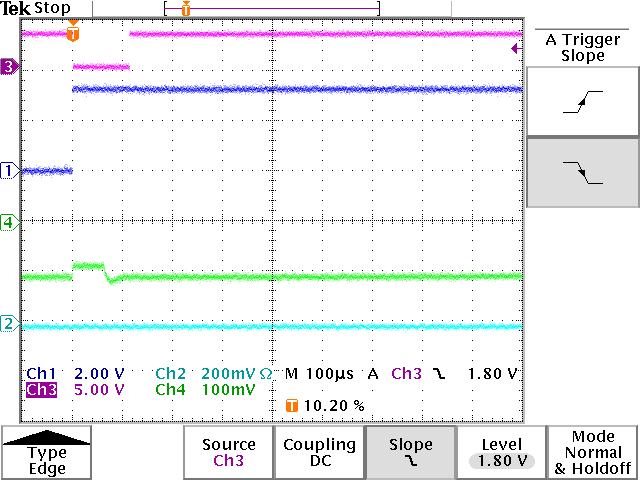

With VCO pre-selection calculated and programmed by our control software and CAP_CODE=47 the usual lock

time is <100us, seen in the Lock Detect signal and of course as seen easily with the spectrum analyzer in Zero-Span Mode

when the ICs AUTOMUTE function is on.

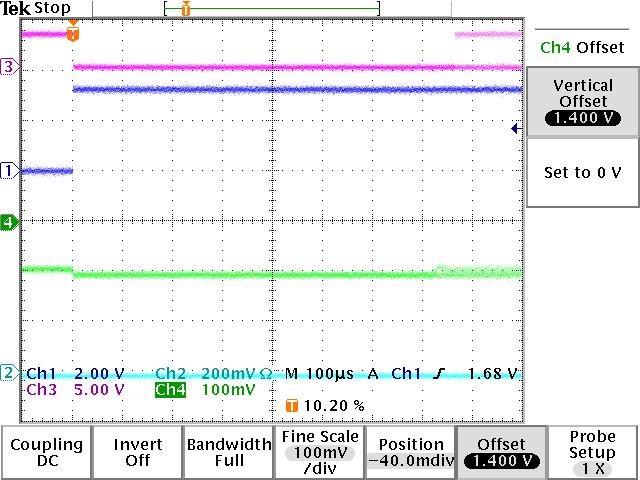

I have monitored the tuning voltage with an oscilloscope. With FCAL active its range is somewhere between slightly above 1.4V

down to around 1.2V.

From my observation, obviously, when FCAL kicks in during frequency change, there is a fixed voltage applied to the

VCO tuning pin, that is Vtune gets slightly below 1.4V and stays constant for a short time (few 10 us).

The critical frequency range - the one with prolonged FCAL times is exactly in this region, where its corresponding

tuning voltage is also slightly below 1.4V.

The H/W is pretty much identical to the EVAL Board, Loop filter 5th order, 30 kHz bandwidth and CPG=24.

Any ideas ? Thank you in advance.

Cheers,

Konstantin

Dresden, Germany