Other Parts Discussed in Thread: TPL5111, , TPS63050

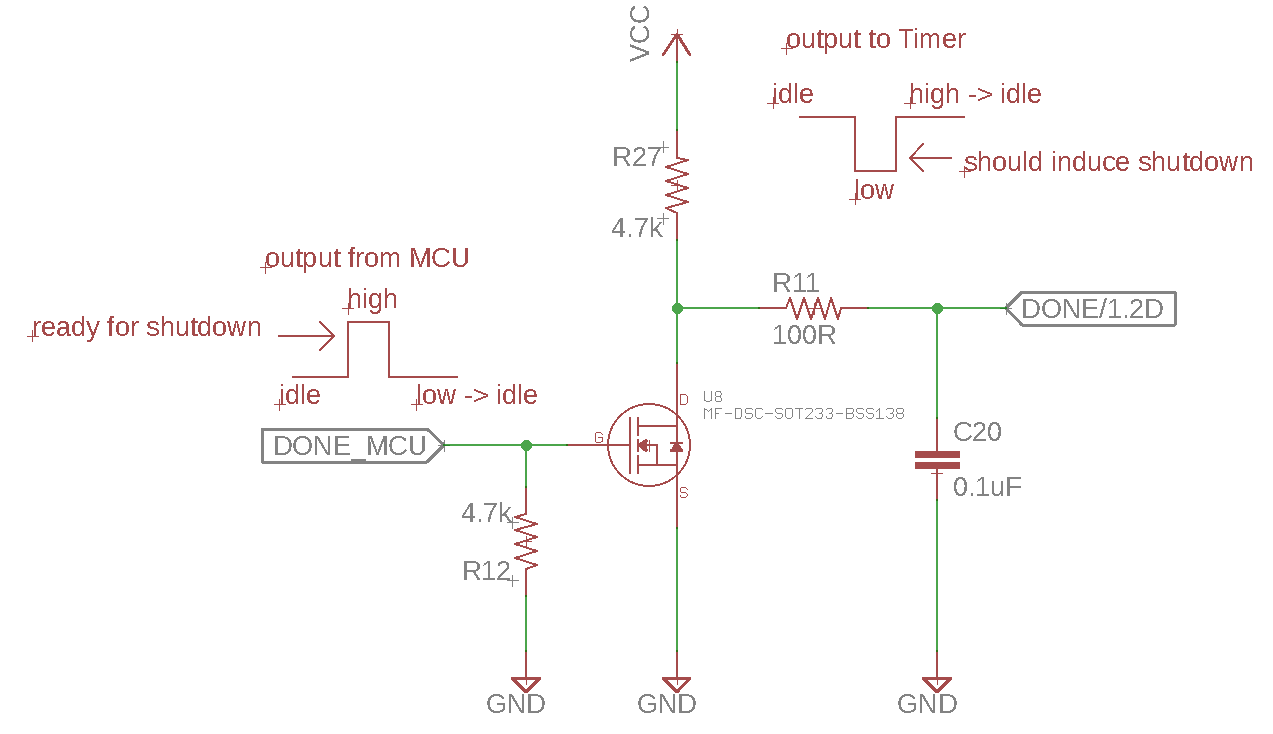

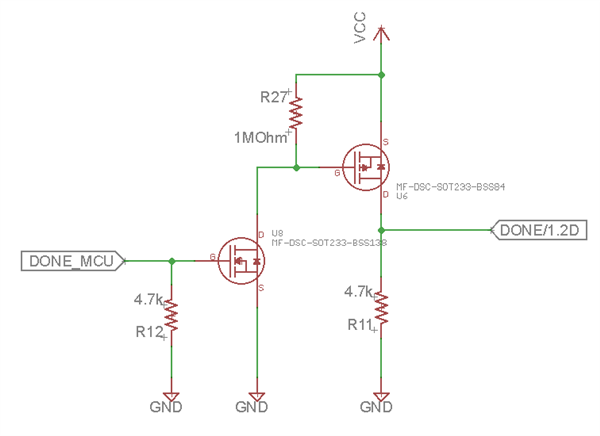

It seems to me like it might be a more robust and simpler approach (than what I've seen in the TPL5111 application notes) to idle the DONE signal to a high state rather than a low state. I've devised the glue logic circuit below to achieve this outcome. With this circuit, the microcontroller has to drive it's "DONE" output HIGH and then LOW to request a timer shutdown.

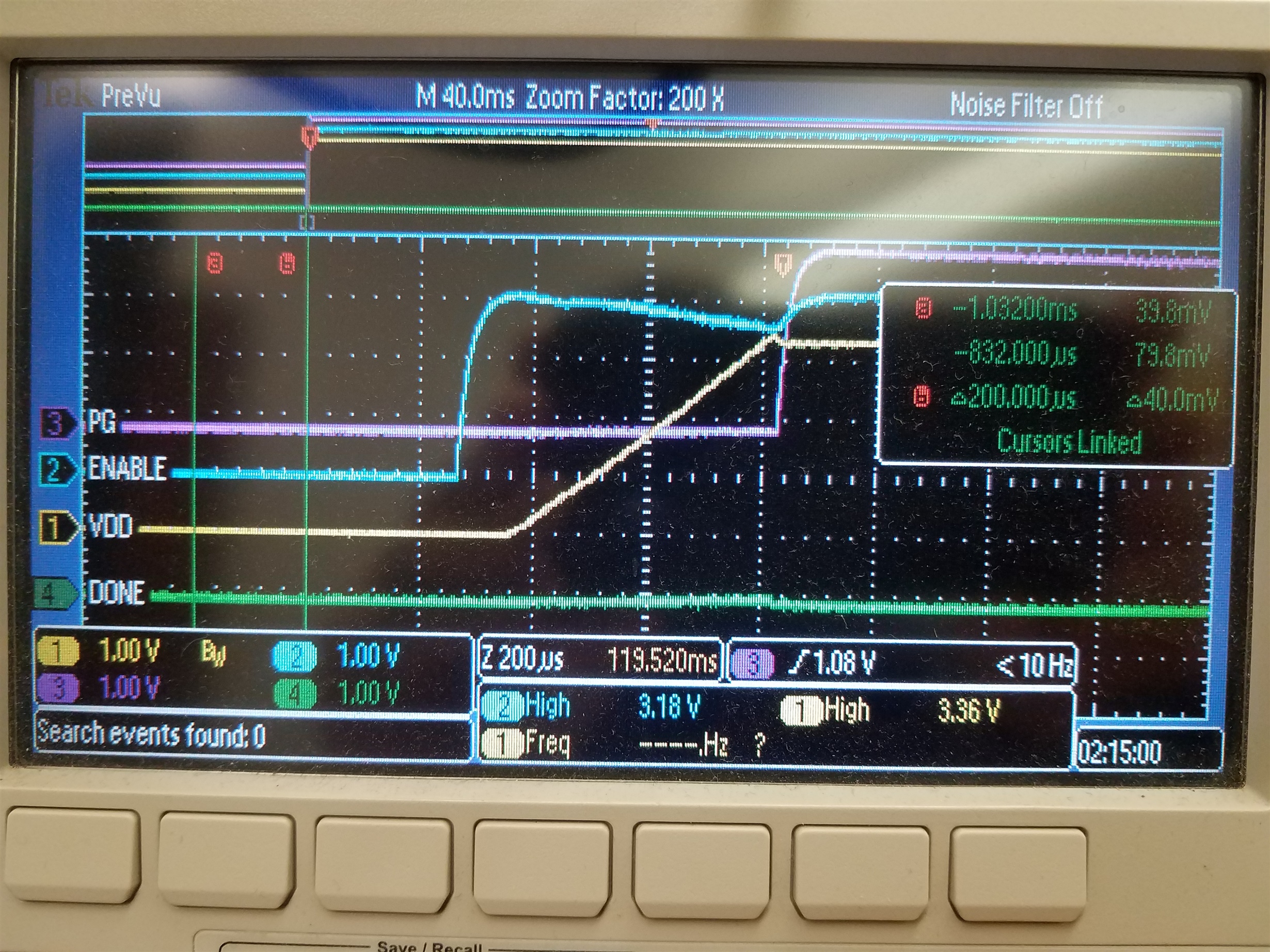

My thinking here is that this topology will be less susceptible to a glitch during system power up (further inhibited by the passive low pass filter on the output stage. the circuit also serves the purpose of isolating the battery voltage domain (VCC in the schematic below) from the system power domain where the MCU signals resides.

Hoping someone from TI can review this design decision and weigh in on whether there are any significant downsides to this approach?