Other Parts Discussed in Thread: CODELOADER,

Hi Team,

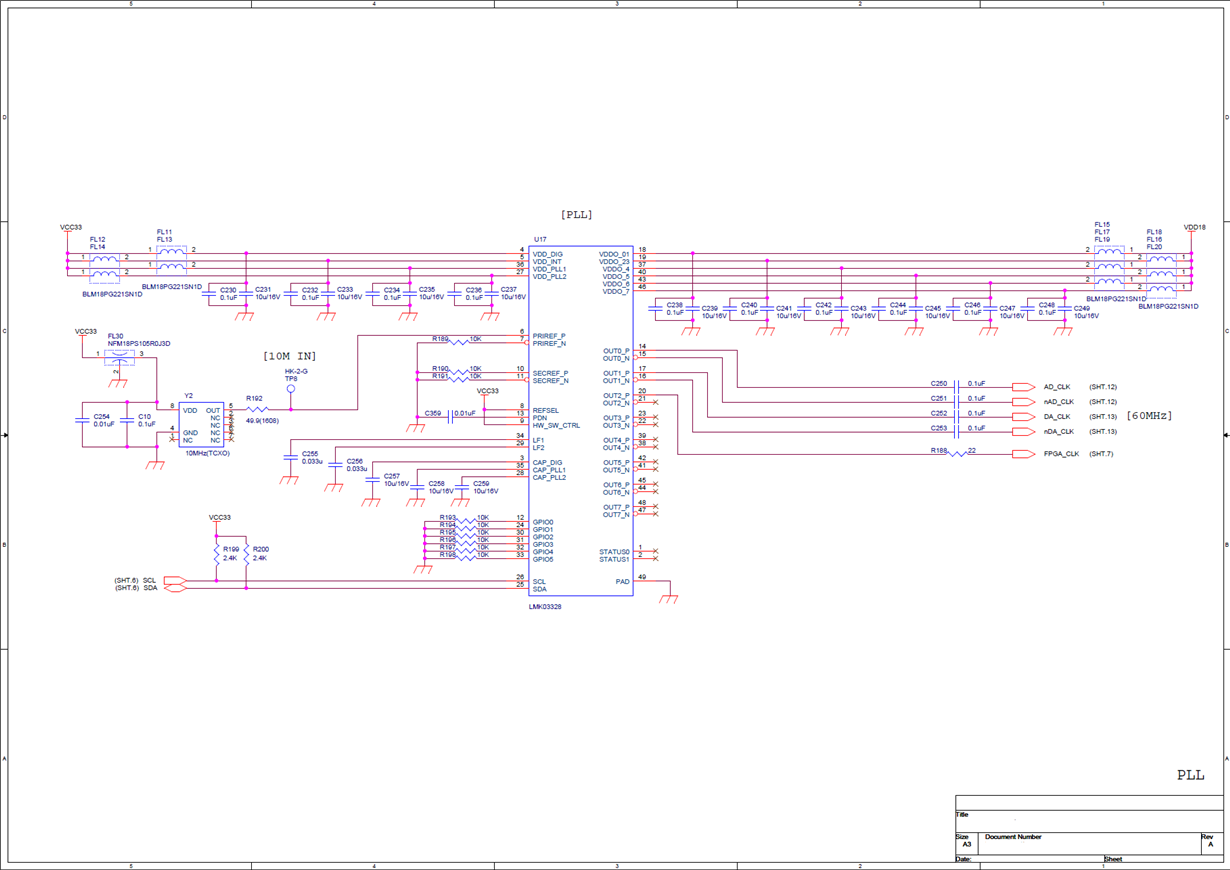

I am having a problem that the PLL Loss of Lock.

It is known that the output of the N divider is stopped.

(Depending on the output of the STATUS0 pin set by R27 [7: 4]=0x4)

The outputs of the R divider and M divider are working normally.

(Similarly, depending on the setting of R27(R28))

How should we debug from here?

WEBENCH data will be attached