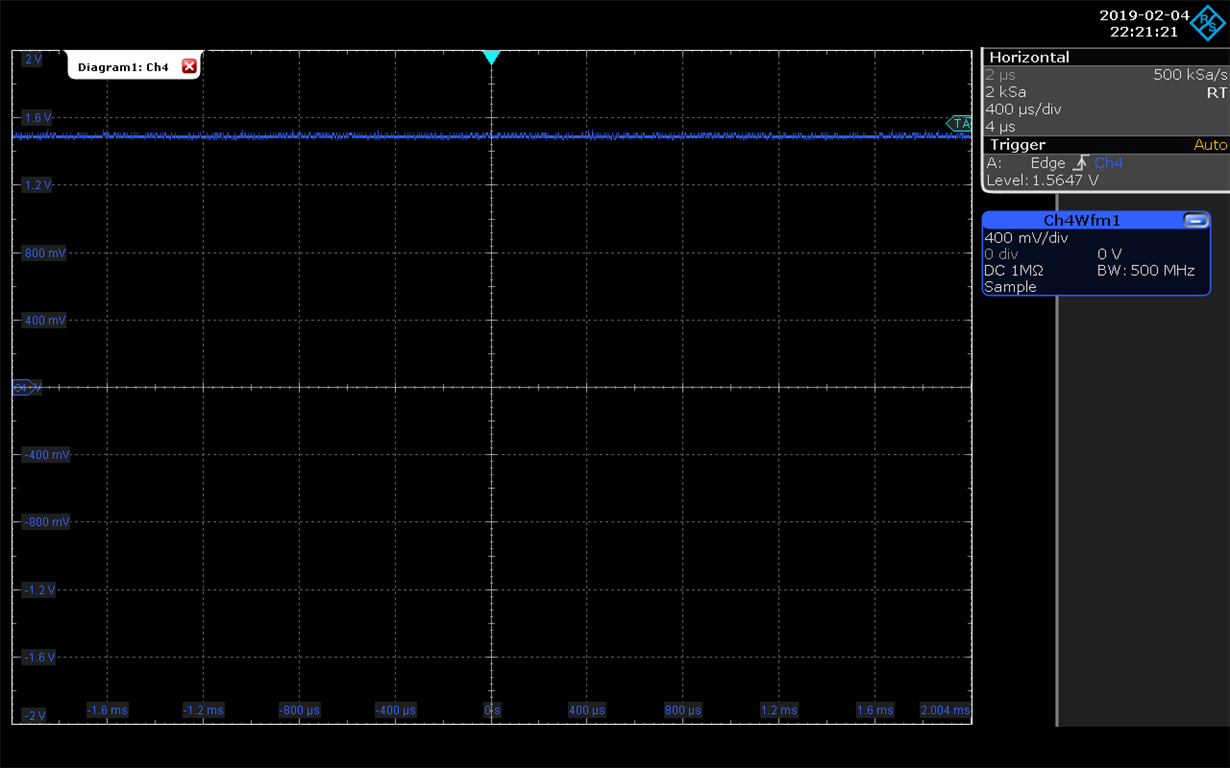

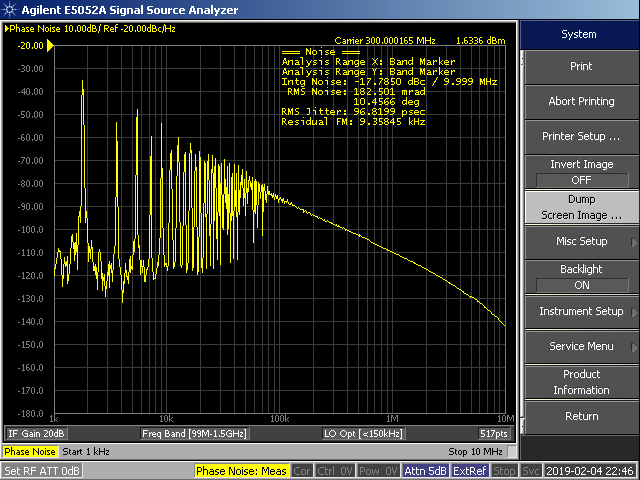

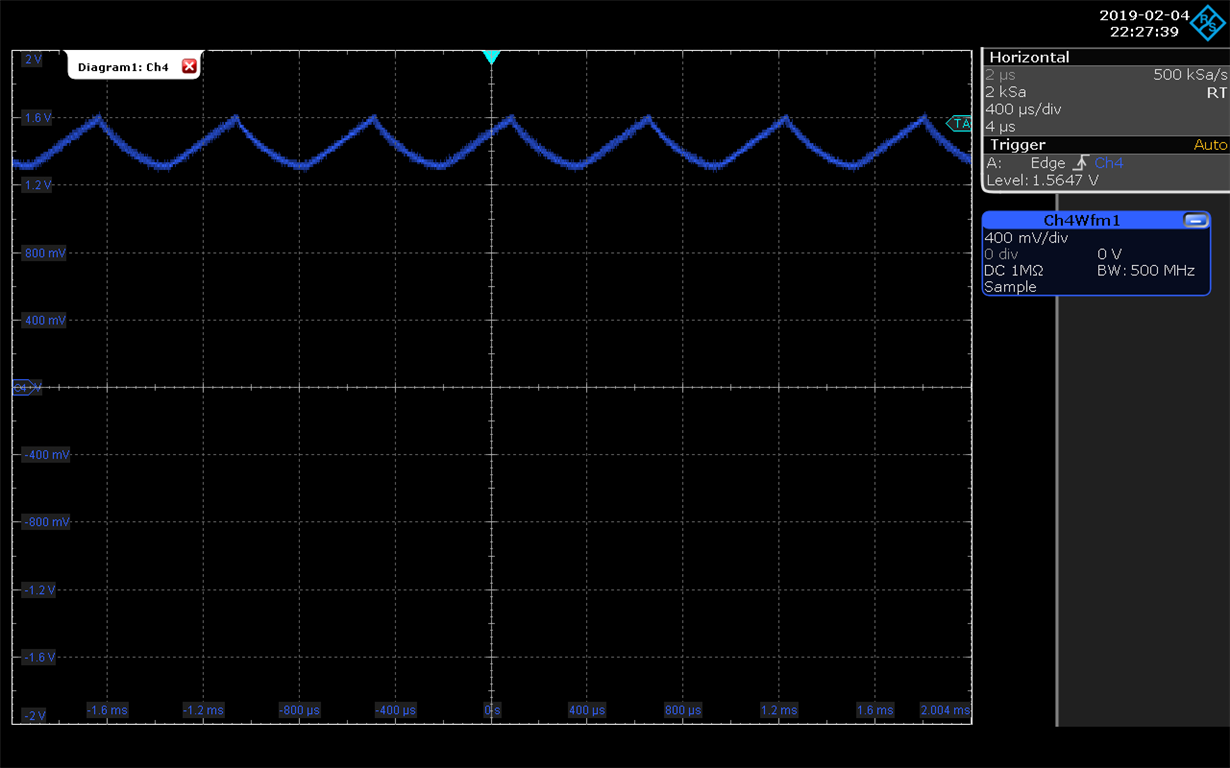

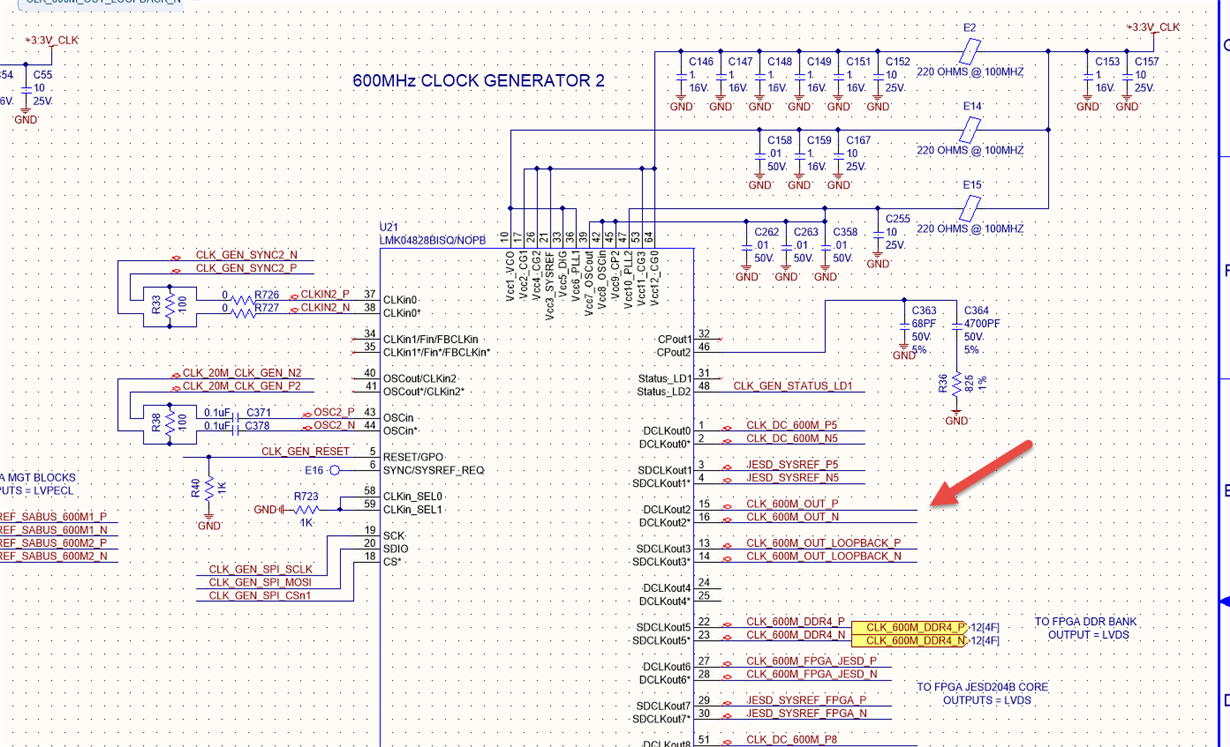

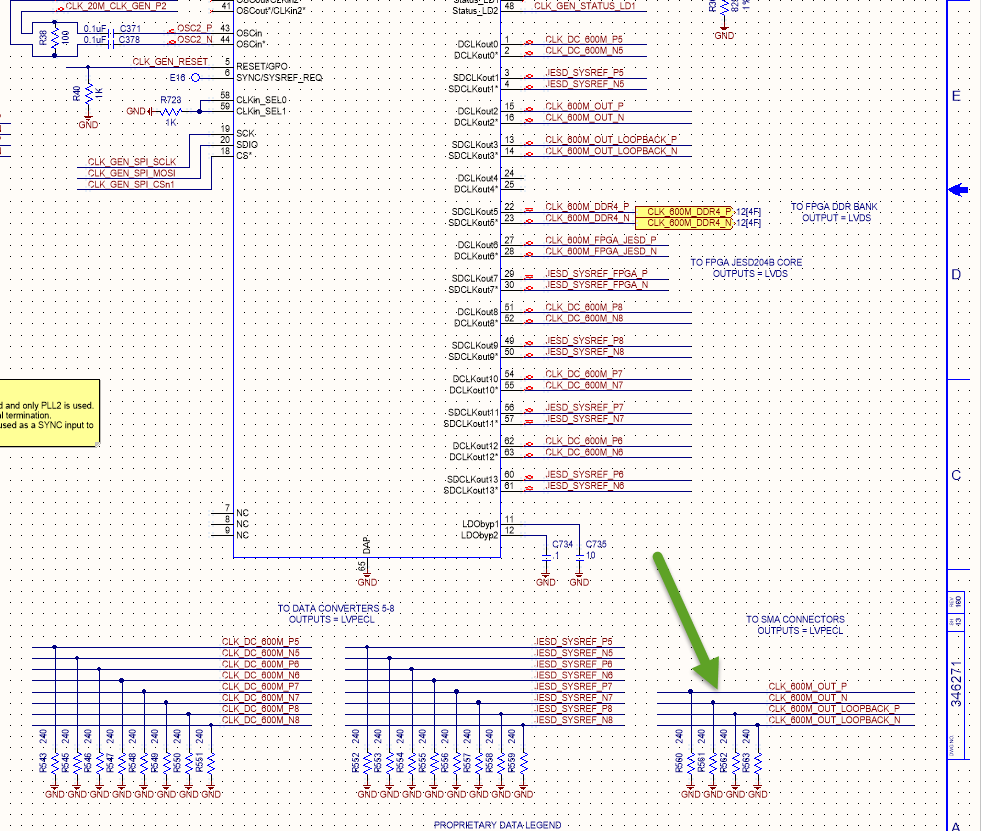

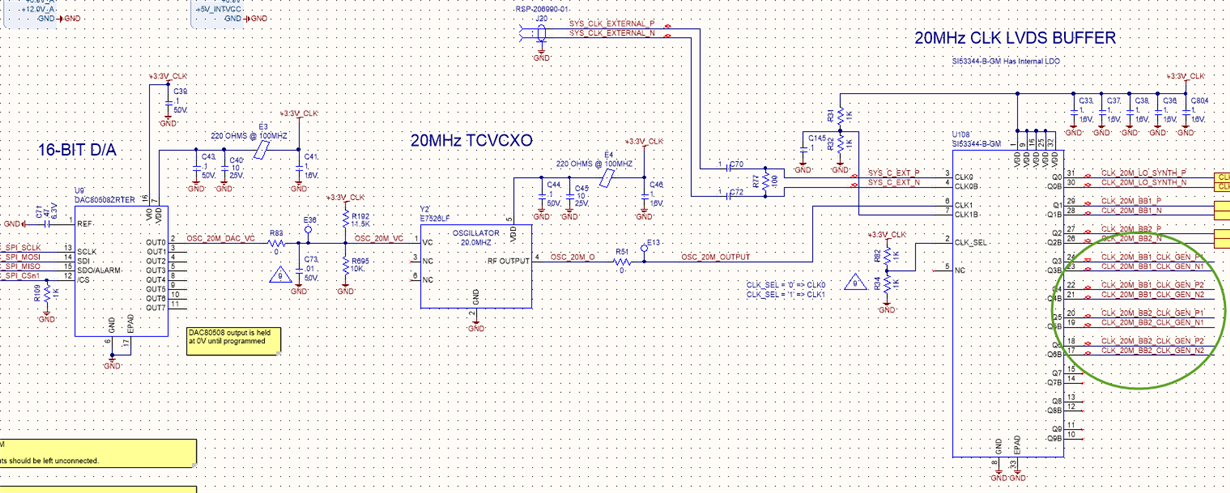

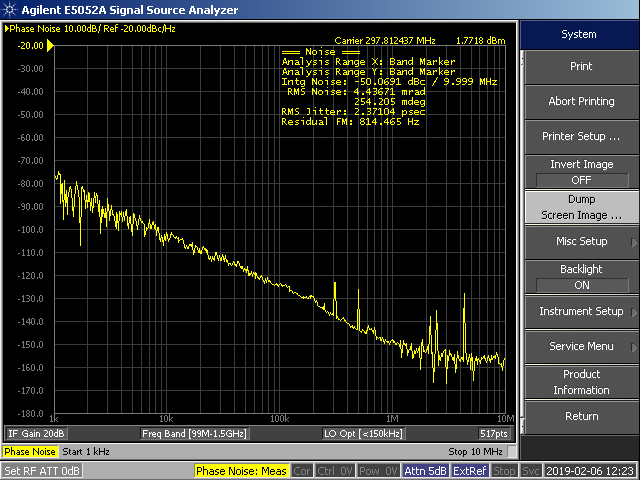

We have a board with two FPGAs and four LMK04828s. Each FPGA programs two of the LMK04828s. However, each of the four LMK04828s share the same oscillator reference which is fanned out using a low jitter LVDS buffer. The two LMK04828s programmed by the first FPGA appear to have acceptable phase noise performance compared to the baseline taken using the evaluation board. However, the other two LMK04828s connected to the second FPGA have terrible phase noise under 100k offset and the charge pump output pin appears to have a sawtooth-like waveform. The first two LMK04828s are identical in schematic design to the second set of LMK04828s and their layouts are very similar, but not 100% the same. I do not understand what could possibly be going on with the second set connected to FPGA 2. They are like this on all boards so its not just a one-off issue. I am including screenshots of the eval board basline which has about 287fs of jitter, an output of one of the second LMK04828 on the first FPGA & its CPout value, and an output of the second LMK04828 on the second FPGA & its CPout value. Also included screenshots of part of the schematic showing the output used to connect to the E5052A. This output has 240 ohm bias resistors since the output is LVPECL. Also shown is a schematic showing the clock reference and fanout buffer.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.