Dears.

Dears.

The LMK04826 has been designed and doing test.

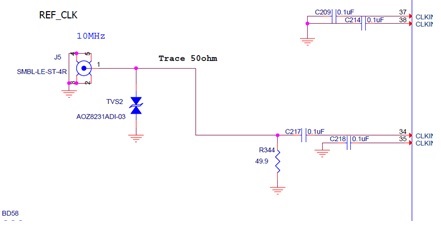

REF_CLK = 10Mhz.

10Mhz is supplied by Signal Generater.

When 10Mhz level is less than 5dBm, PLL lock does not work.

Even if R344 is removed and a 10Mhz level is input up to 0dBm, it becomes PLL Lock.

Why does the PLL Lock level differ?

Is 50 Ohm necessary?

How do I get a 10Mhz level to -3dBm to PLL lock?

Thank you