Hi,

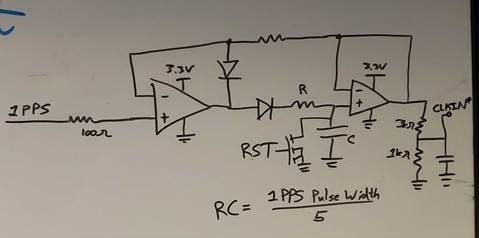

Please help me to review the schematics of LMK00105.

Our Target application is as follows,

We have one 1PPS LVCMOS (3.3/2.5) signal comes from GPS receiver and we want to split this 1PPS signal to 2 LVCMOS 1.8V signal.

What all LVCMOS terminations have to be given and how to decide?..