Other Parts Discussed in Thread: CDCVF2505,

Hi TI Expert,

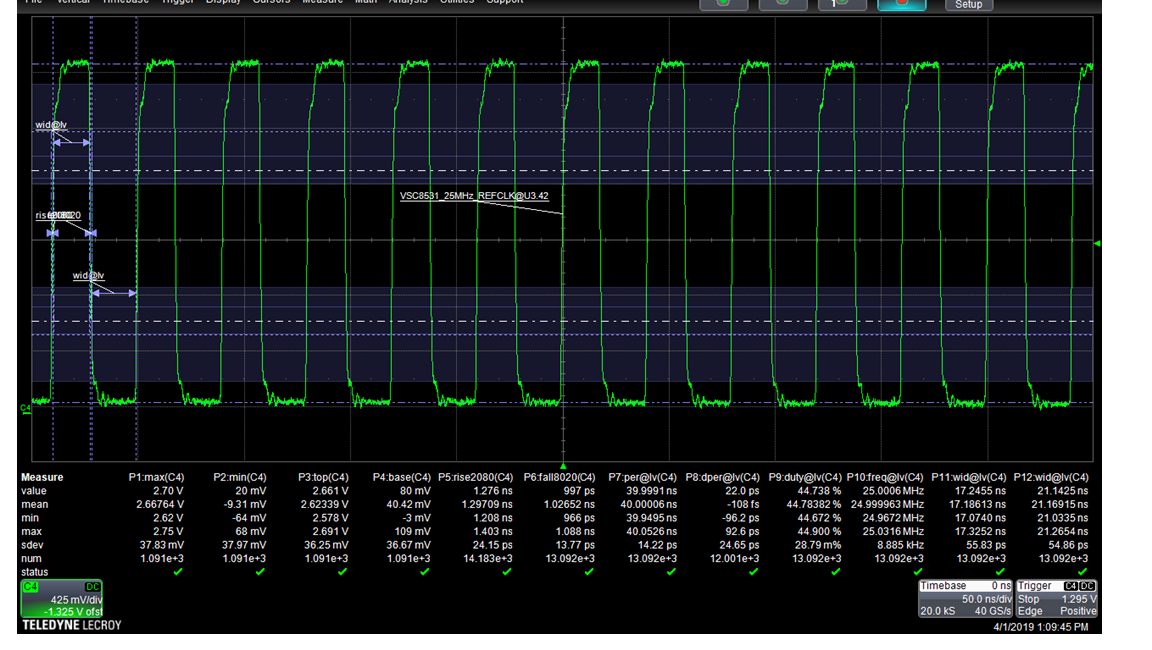

In our design, CDCV304PW had be used for fan-out four 25MHz clock to CPU/CPLD/FPGA/PHY, we found 25MHz output duty cycle is 44.692%~45.150%, which not meet our applycation (45%~55%),

Anymore, the 25MHz intput duty cycle is about 50%, do you have any better suggestion how to promote the duty cycle?

I also attached my schematic and test waveform for your checking, thanks!

Bruce