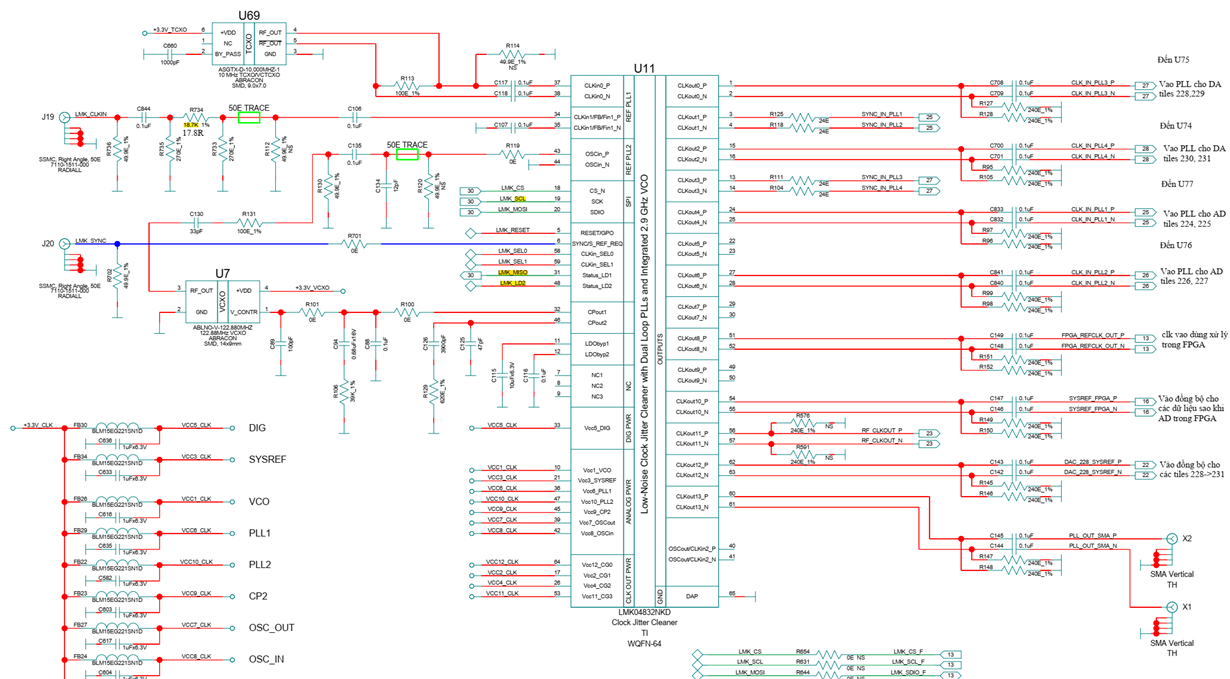

Other Parts Discussed in Thread: LMK04832

Dear Sir ! I use LMK04832 device in my board and need to configure it operate in Dual loop mode. But i can not get PLL2 DLD (Status_LD2) lock. When i tried to use in single loop mode, the PLL2 DLD (Status_LD2) locked, and i got the correct outputs frequency. Please look into my setting and give me some recommendations ! thank you !