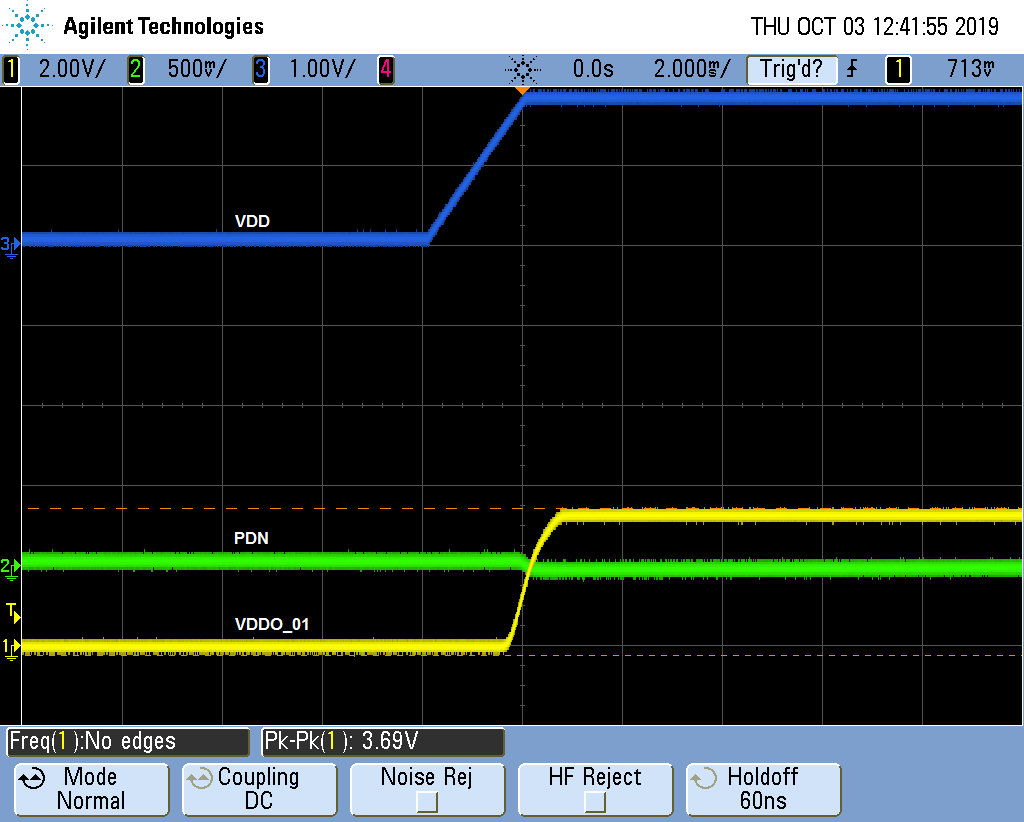

To ensure the 10MHz OCXO output stable before the LMK03328 PLLs lock, we add a 10uF cap to the PDN pin.

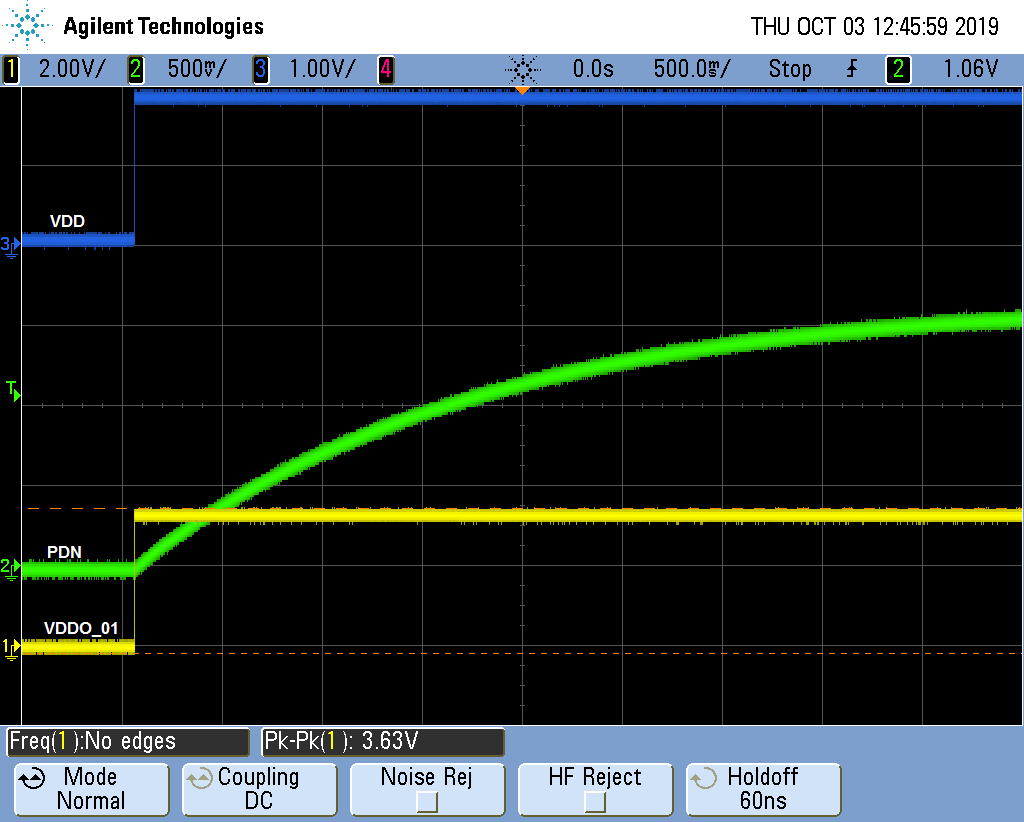

Most of the time, it power up ok with output clock but not always like that.

We are seeing some of this LMK03328 power up with no output clock at all. By power off then on, it will output clock.

We need to understand why and how this happen? How to fix this issue?

Thanks,

Laurie