Other Parts Discussed in Thread: LMX2594, LMX2491, LMX2572EVM, LMX2572, LMX2492

Hi TI expert,

We have a LMX2594EVM and we want to use it to generate a linear frequency ramp from 100 MHz to 1.6 GHz. Is it possible to generate a continuous and smooth ramp with LMX2594?

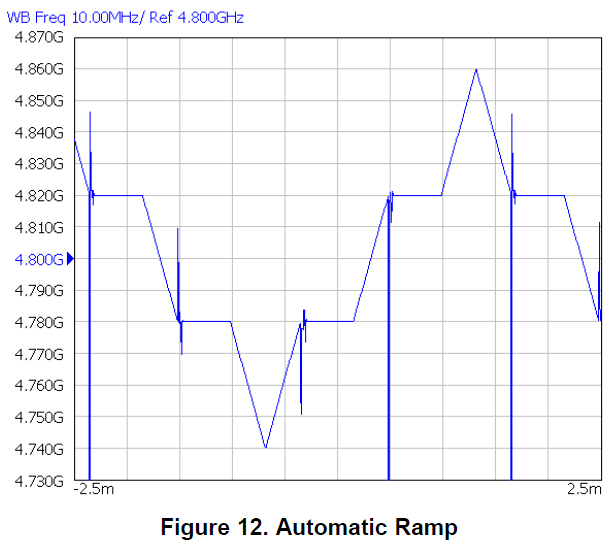

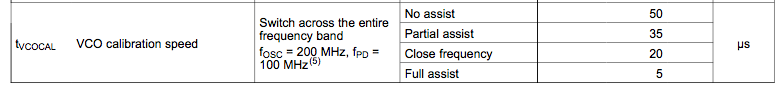

We know the VCO calibration is a limiting factor and we can try to use the "Fully Assist" mode. But I found there would be a 1-2 microsecond gap when VCO core is changing.

https://e2e.ti.com/support/clock-and-timing/f/48/t/664879?tisearch=e2e-sitesearch&keymatch=lmx2594%25252525252520ramp%25252525252520full%25252525252520assist

e2e.ti.com/.../Fast-frequency-switching-full-assist.pdf

Is it possible that we can do this without this transition time?

If possible, could you send us an example code that we can load into TICSPRO to generate such a ramp (100 MHz to 1.6 GHz)? We just want to see the code structure. You can use your own calibration and we can do this offline by ourselves.