Hello there,

I've been trying to synchronize two LMX2594 chips at 4.096GHz. The output frequency is 4.096GHz before I toggle sync. However, after I toggle the sync bit toggled the output frequency becomes unstable and shows almost a square wave characteristic. Since the included divide can only take value of 4 and 6. How is sync possible for output frequency at 4.096GHz? The highest VCOband 7 max at 15GHz, with included divide=4 this gives 3.75GHz. Could anyone from TI confirm whether it is possible to synchronize two LMX2594 at 4.096GHz? If it is possible, what is the correct procedure for synchronization in this case as this is a special case that VCO needs to be divided by 2.

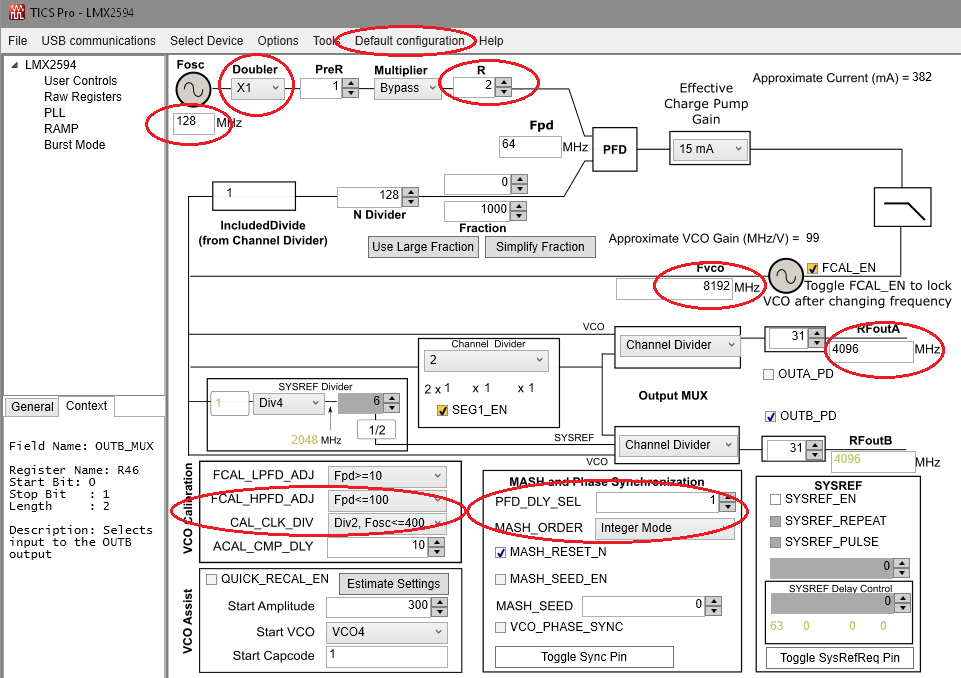

Let me list my settings for initial configuration

fOsc in is 128MHz, expected VCOband is 1 and VCO should run at 8.192GHz

OSC_2X = 0 (disabled)

PLL_R_PRE = 1,

PLL_R = 1,

Mult = 1 (bypass)

CHDIV = 0 (VCO divide by 2)

PLL_N = 64.

VCO_SEL = 1

MASH_ORDER = 0

VCO_DACISET_STRT and VCO_CAPCTRL_STRT are set according to the formula listed in the datasheet.

VCO_PHASE_SYNC = 0 and

FCAL_EN = 1.

The above setup gives me the correct frequency output prior to sync. I then tried the following:

After the device is programmed, I then set PLL_N to 16 and VCO_PHASE_SYNC to 1. Reason setting PLL_N to 16 is because the Included_divide after sync is 4.

I also tried to program PLL_N = 16 and VCO_PHASE_SYNC = 1 in the initial configuration but that didn't work either.

Thanks,

Li